### **TECHNICAL MANUAL**

OPERATOR'S, ORGANIZATIONAL,

DIRECT SUPPORT, GENERAL SUPPORT, AND

DEPOT MAINTENANCE MANUAL

FOR

INTERCEPT GROUP COUNTERMEASURES RECEIVING SET AN/FLR-9(V7)/(V8)

F & M SYSTEMS CO.

**HEADQUARTERS, DEPARTMENT OF THE ARMY**

## TM 32-5895-234-15

HEADQUARTERS DEPARTMENT OF THE ARMY WASHINGTON, DC, 4 JUNE 1976

TM 32-5895-234-15, 4 JUNE 1976, is a reprint of ASA Instruction Manual 32-5895-234-15, 1 November 1972. Published for the use of all concerned.

Reproduction for the non-military use of the information or illustrations contained in this publication is not permitted without specific approval of the issuing service. The policy for use classified Publications is established for the Army in AR 350-5.

Technical manuals are normally distributed promptly after printing. Date(s) shown on the title page (lower right) are for identification only. This is not a distribution date. Processing time sometimes causes distribution to only appear to have been delayed.

#### LIST OF EFFECTIVE

### **INSERT LATEST CHANGED PAGES. DESTROY SUPERSEDED PAGES**

NOTE: The portion of the text affected by the changes is indicated by a vertical line in the outer margins of the page. Changes to illustrations are indicted by miniature pointing hands.

#### TOTAL NUMBER OF PAGES IN THIS PUBLICATION IS 185 CONSISTING OF THE FOLLOWING

| Page No.         | Change No. | Page No.              | Change No. |

|------------------|------------|-----------------------|------------|

| Volume 1         |            |                       |            |

| Title            | 2          | 5-5                   | 1          |

| A                | 2          | 5-6                   | 1          |

| i-ii             | 0          | 5-7                   | 2<br>2     |

| iii              | 2          | 5-8                   | 2          |

| iv               | 0          | 5-8a                  | 2<br>2     |

| 1-1 - 1-4        | 0          | 5-8b (Blank)          | 2          |

| 1-5              | 2          | 5-9                   | 0          |

| 1-6 - 1-13       | 0          | 5-10                  | 1          |

| 1-14             | 2          | 5-11 - 5-16           | 0          |

| 1-15 - 1-31      | 0          | 5-17                  | 1          |

| 1-32 (Blank)     | 0          | 5-18                  | 0          |

| 2-1 ` ′          | 0          | 5-19                  | 1          |

| 2-2              | 2          | 5-20 - 5-33           | 0          |

| 2-3              | 0          | 5-34 (Blank)          | 0          |

| 2-4              | 2          | 6-1 ` ´               | 1          |

| 2-4a             | 2          | 6-2                   | 1          |

| 2-4b (Blank)     | 2          | 6-3                   | 0          |

| 3-1 <sup>`</sup> | 1          | 6-4 (Blank)           | 0          |

| 3-2 - 3-4        | 0          | 7-1 - 7-4 ´           | 0          |

| 3-5              | 1          | **7-5/7-6 - 7-63/7-64 | 0          |

| 3-6 - 3-14       | 0          |                       |            |

| 4-1 - 4-20       | 0          | Volu                  | me 2       |

| **4 -21/4-22     | 0          | 8-1 - 8-2             | 0          |

| 4-23 - 4-50      | 0          | 8-3                   | 2          |

| 5-1 - 5-4        | 0          | ***8-4 (Blank)        | 0          |

|                  | -          | 9-1 - 9-2             | 0          |

|                  |            | 9-3                   | 2          |

|                  |            | ****9-4 (Blank)       | 0          |

|                  |            | ο · (Ειαιιίί)         | •          |

- Zero in this column indicates original page.

- Foldout pages are double numbered -(7-5/7-6) indicating a blank on reverse side.

- • Parts list and wire cable lists are not included in total pages.

Upon receipt of the second and subsequent changes to this publication personnel responsible for maintaining this publication in current status will ascertain that all previous changes have been received and incorporated. Action should be taken if the publication is incomplete.

# **TABLE OF CONTENTS**

# **VOLUME 1**

| Section |              |                                                   | Page |  |  |  |

|---------|--------------|---------------------------------------------------|------|--|--|--|

| I.      | DESCI        | DESCRIPTION                                       |      |  |  |  |

|         | 1-1.         | Scope of Manual                                   | 1-1  |  |  |  |

|         | 1-2.         | Purpose of Manual                                 | 1-1  |  |  |  |

|         | 1-3.         | Description and Purpose                           | 1-1  |  |  |  |

|         | 1-4.         | Leading Particulars                               | 1-3  |  |  |  |

|         | 1-5.         | Capabilities and Limitations                      | 1-4  |  |  |  |

|         | 1-6.         | Equipment Supplied                                | 1-4  |  |  |  |

|         | 1-7.         | Equipment Required But Not Supplied               | 1-5  |  |  |  |

|         | 1-8.         | Model Differences                                 | 1-5  |  |  |  |

|         | 1-9.         | Reference Designation                             | 1-5  |  |  |  |

|         | 1-10.        | List of Publications                              | 1-31 |  |  |  |

| II.     | INSTA        | LLATION                                           | 2-1  |  |  |  |

|         | 2-1.         | Scope                                             | 2-1  |  |  |  |

|         | 2-2.         | Unpacking                                         | 2-1  |  |  |  |

|         | 2-3.         | Inspection                                        | 2-1  |  |  |  |

|         | 2-4.         | Equipment Floor Space                             | 2-2  |  |  |  |

|         | 2-5.         | Installation                                      | 2-2  |  |  |  |

|         | 2-6.         | Initial Adjustments                               | 2-2  |  |  |  |

| III.    | OPER         | OPERATION                                         |      |  |  |  |

|         | 3-1.         | Scope                                             | 3-1  |  |  |  |

|         | 3-2.         | Controls and Indicators                           | 3-1  |  |  |  |

|         | 3-3.         | Turn-On Procedures                                | 3-1  |  |  |  |

|         | 3-4.         | Operating Procedures                              | 3-1  |  |  |  |

|         | 3-5.         | Turn-Off                                          | 3-9  |  |  |  |

|         | 3-6.         | Emergency Turn-Off                                | 3-9  |  |  |  |

|         | 3-7.         | Bsu/Biu Operating Characteristics                 | 3-9  |  |  |  |

|         | 3-8.         | Special Project Bsu/Biu Operating Characteristics | 3-13 |  |  |  |

| IV.     | THEO         | RY OF OPERATION                                   | 4-1  |  |  |  |

|         | 4-1.         | Scope                                             | 4-1  |  |  |  |

|         | 4-2.         | Intercept Group Functional Description            | 4-1  |  |  |  |

|         | 4-3.         | Intercept Group Principles of Operation           | 4-1  |  |  |  |

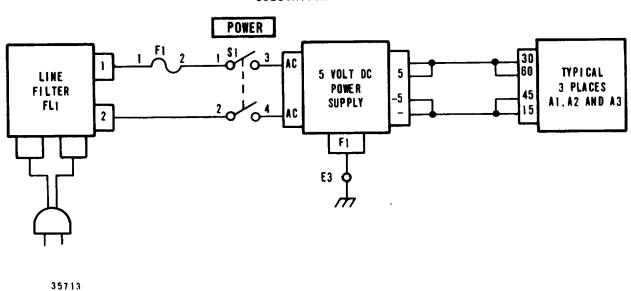

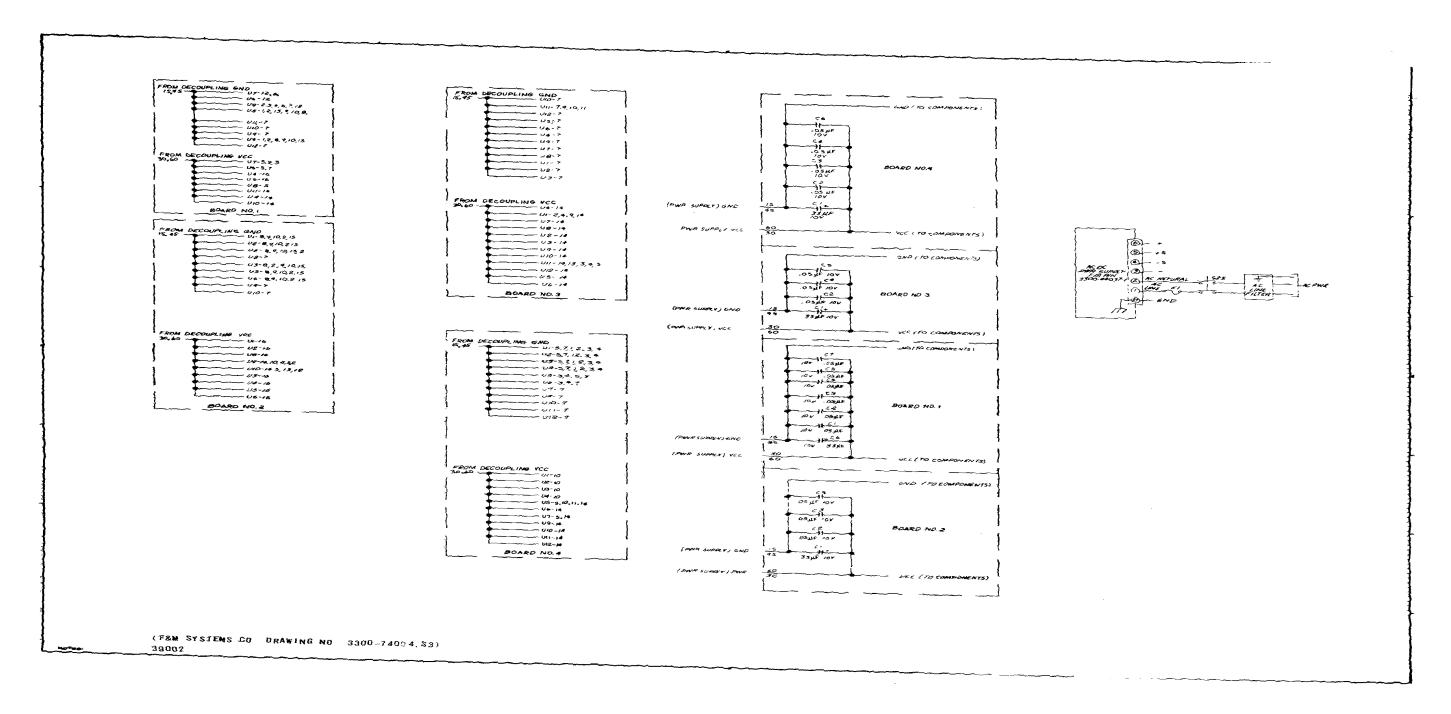

|         | 4-4.         | Power Distribution                                | 4-4  |  |  |  |

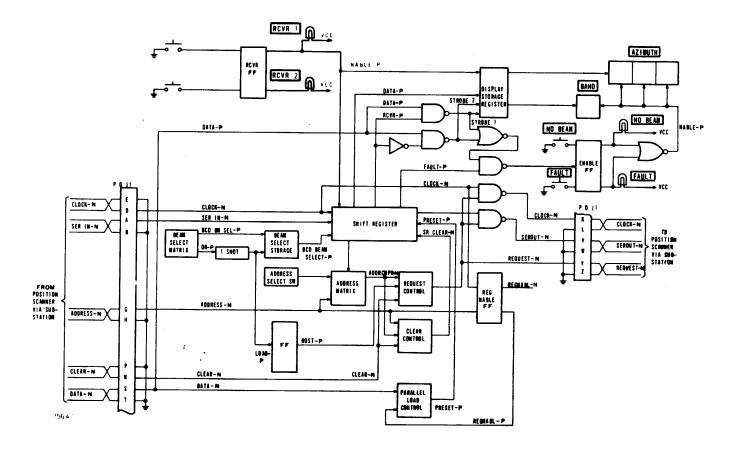

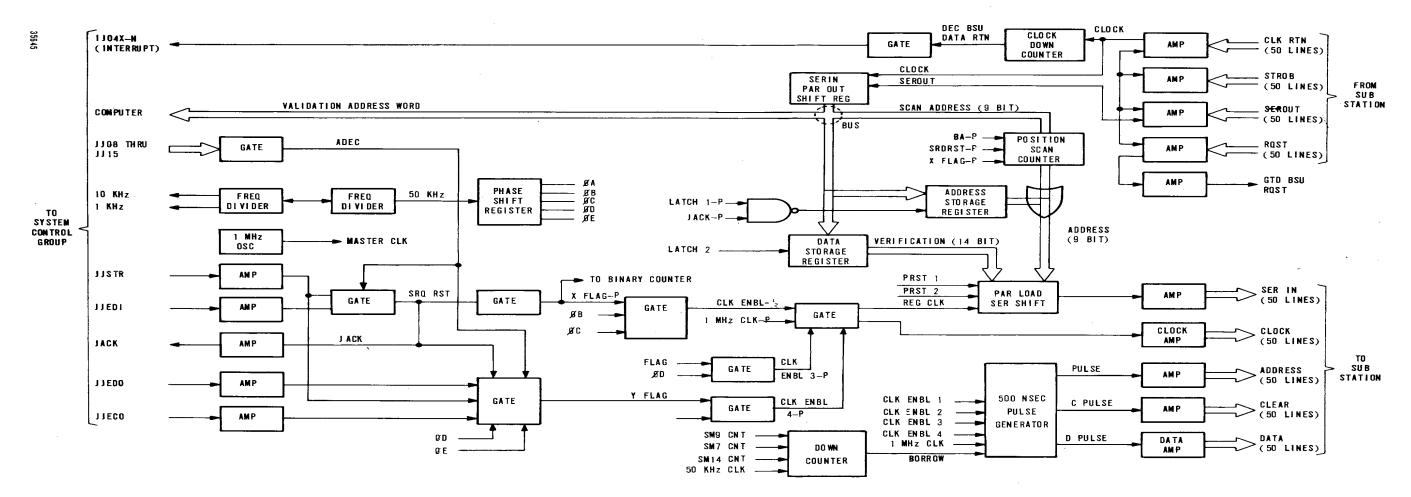

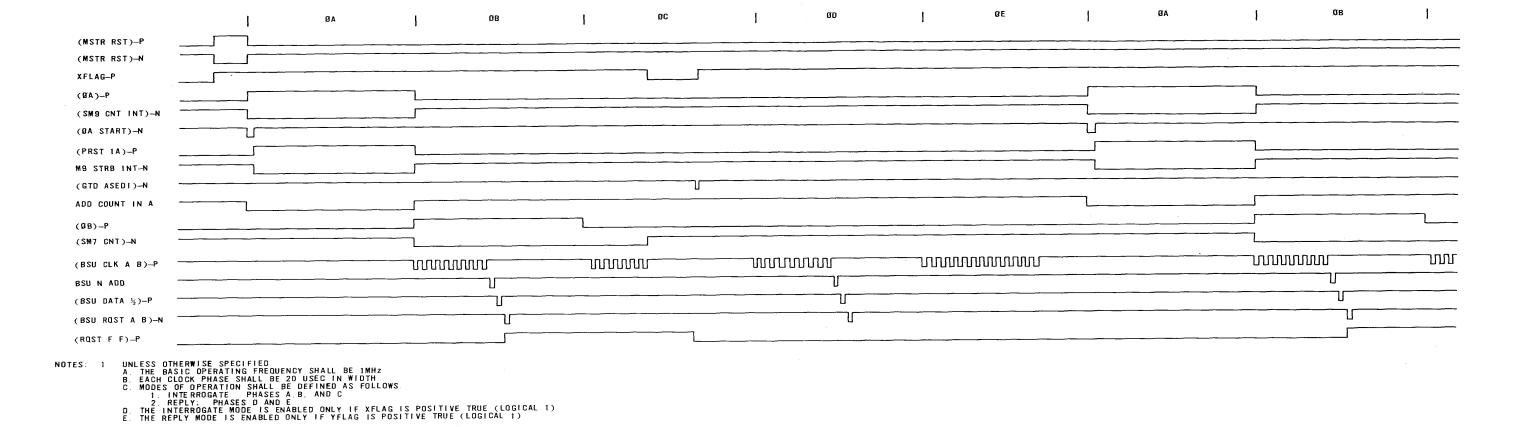

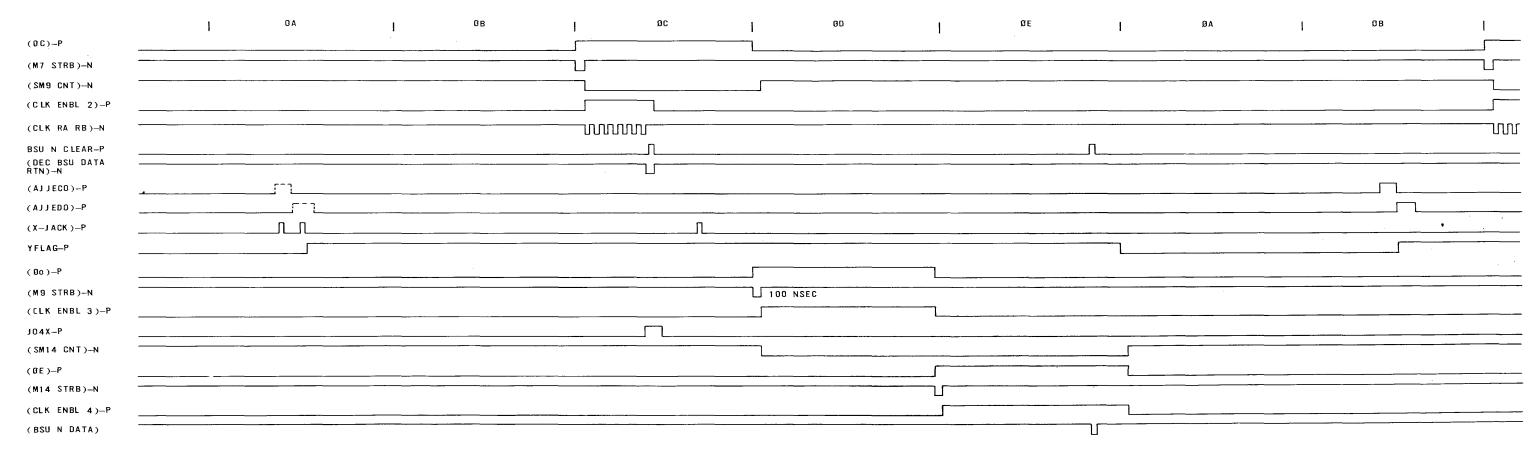

|         | 4-5.         | Bsu/Biu Detailed Description                      | 4-4  |  |  |  |

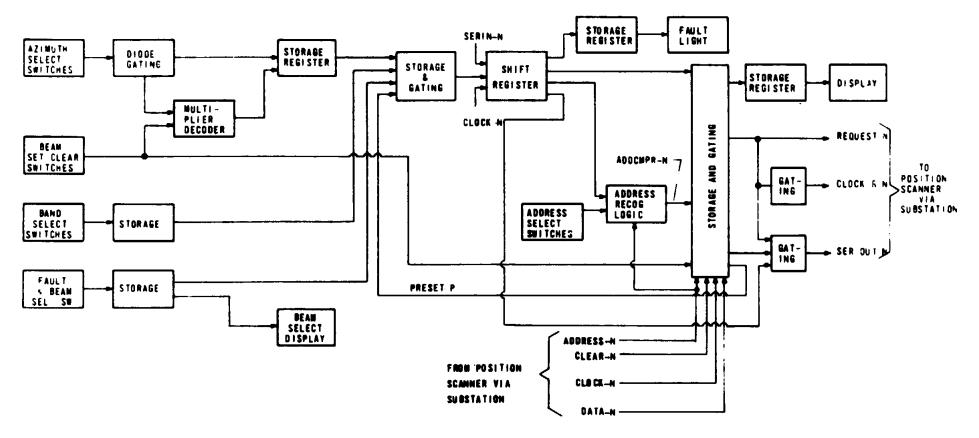

|         | 4-6.         | Special Project Bsu/Biu Detailed Description      | 4-12 |  |  |  |

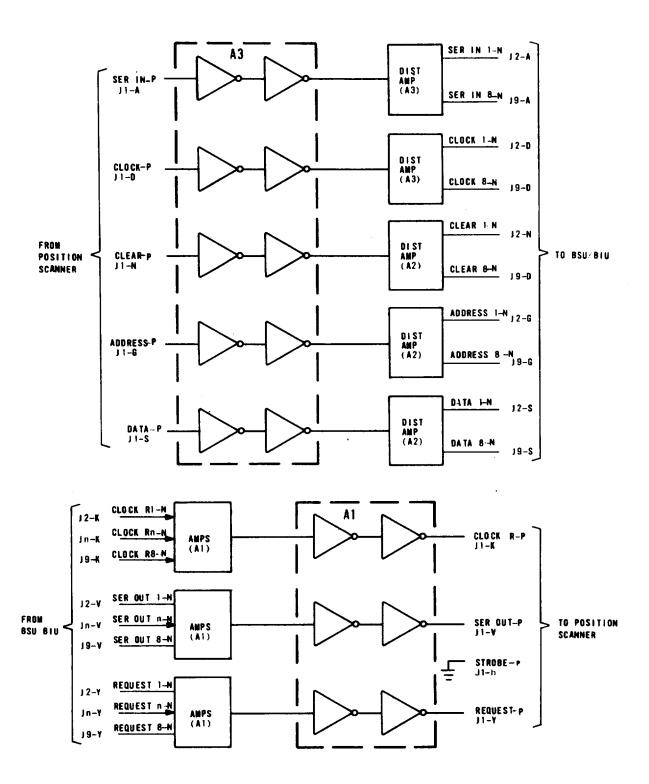

|         | 4-7.         | Substation                                        | 4-17 |  |  |  |

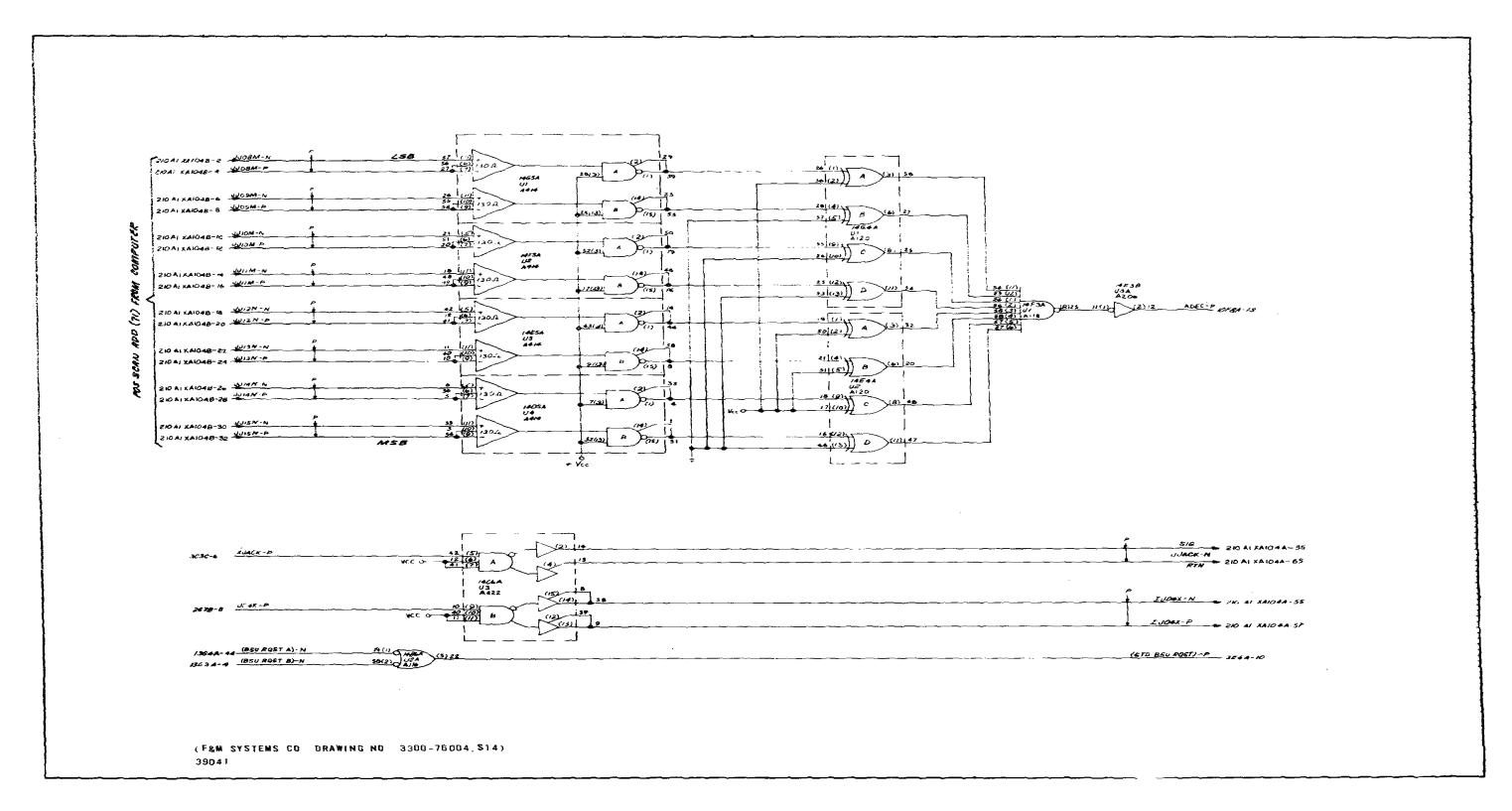

|         | 4-8.         | Position Scanner                                  | 4-19 |  |  |  |

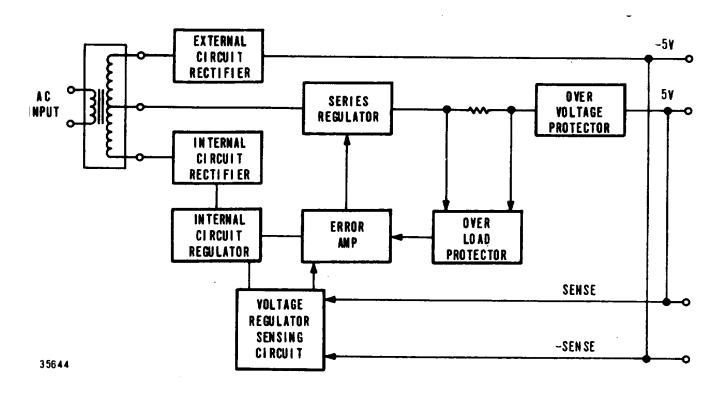

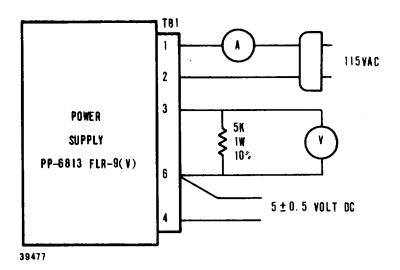

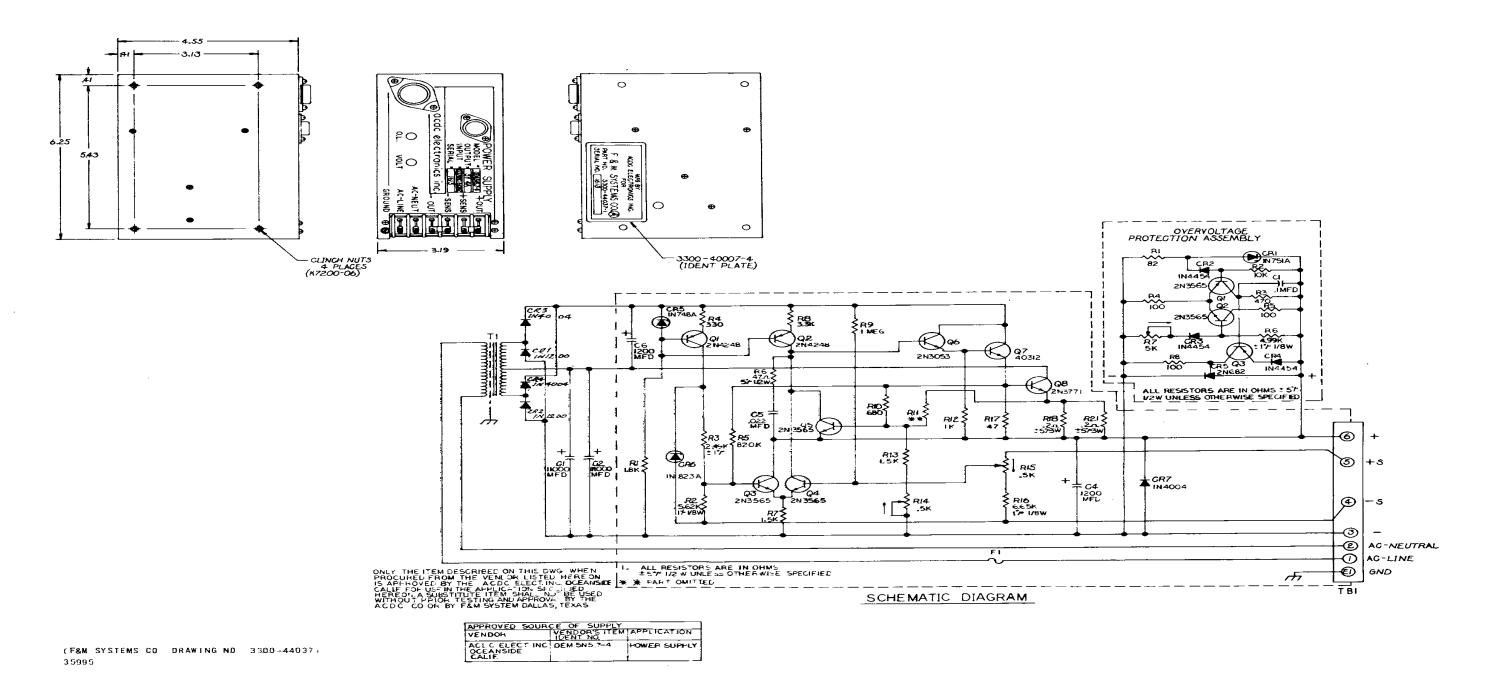

|         | <b>4-9</b> . | Power Supply, PP-6813/FLR-9(V)                    | 4-27 |  |  |  |

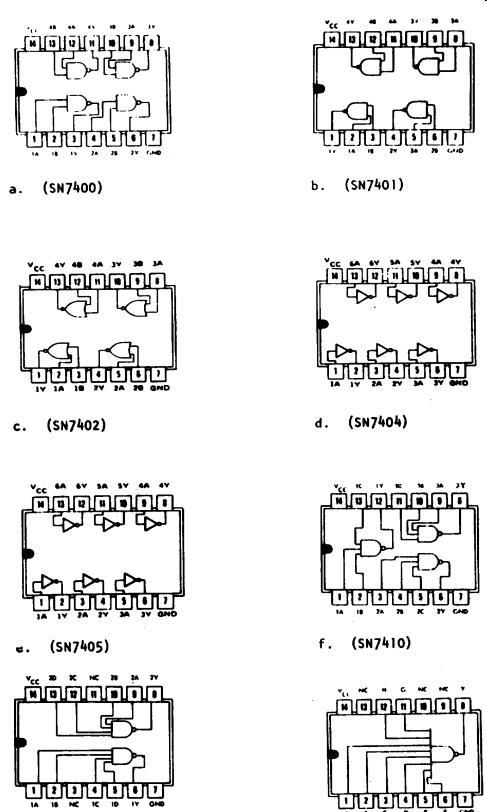

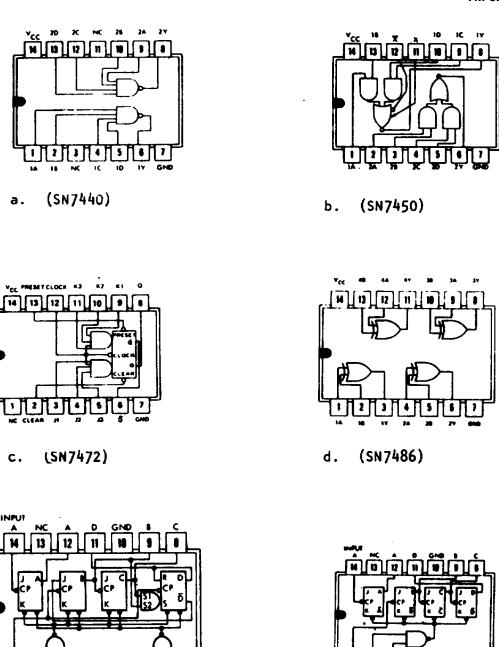

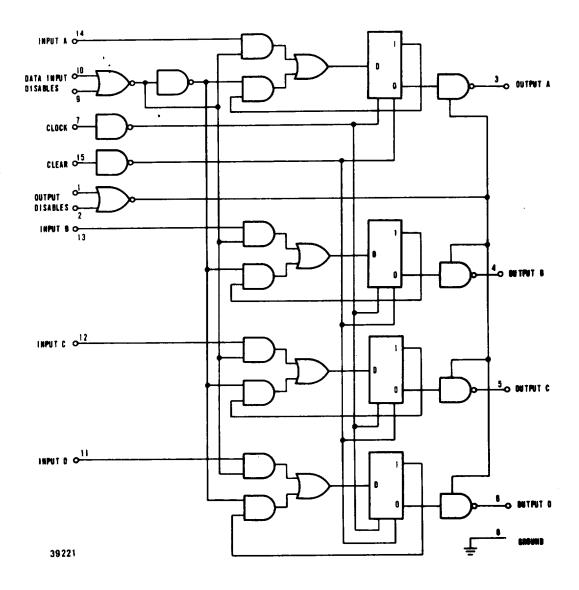

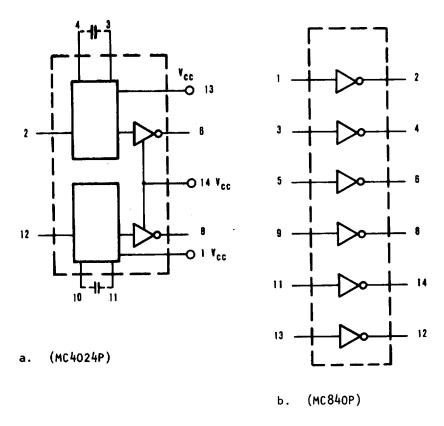

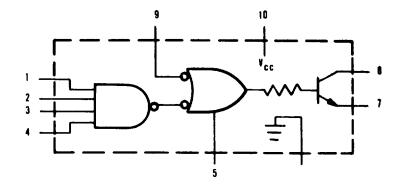

|         | 4-10.        | Detailed Integrated Circuit Description           | 4-28 |  |  |  |

# **TABLE OF CONTENTS (Continued)**

| Section |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| V.      | MAIN                                                                                                                                 | TENANCE AND REPAIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-1                                                                                                                                 |

|         | 5-1.<br>5-2.<br>5-3.<br>5-4.<br>5-5.<br>5-6.<br>5-7.<br>5-8.<br>5-10.<br>5-11.<br>5-12.<br>5-13.<br>5-14.<br>5-15.<br>5-16.<br>5-17. | Scope Non-Maintenance Items Preventive Maintenance Maintenance Test Equipment Special Maintenance Tools Corrective Maintenance Logical Troubleshooting Procedures Intercept Group Operational Tests Bsu/Biu Performance Tests Bsu/Biu Troubleshooting Special Project Bsu/Biu Performance Tests Special Project Bsu/Biu Troubleshooting Substation Performance Tests Substation Performance Tests Substation Bsu/Biu Troubleshooting Position Scanner Troubleshooting Power Supply Troubleshooting Repair Procedures Alignment and Adjustment Minimum Performance Standards | 5-1<br>5-1<br>5-1<br>5-2<br>5-3<br>5-3<br>5-3<br>5-4<br>5-7<br>5-10<br>5-12<br>5-15<br>5-16<br>5-19<br>5-20<br>5-26<br>5-27<br>5-32 |

| VI.     | DEPO                                                                                                                                 | T INSPECTION STANDARDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-1                                                                                                                                 |

|         | 6-1.<br>6-2.<br>6-3.<br>6-4.<br>6-5.<br>6-6.                                                                                         | Scope Tests Test Equipment Bsu/Biu Operational Test Special Project Bsu/Biu Operational Test Substation Operational Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-1<br>6-1<br>6-2<br>6-3                                                                                              |

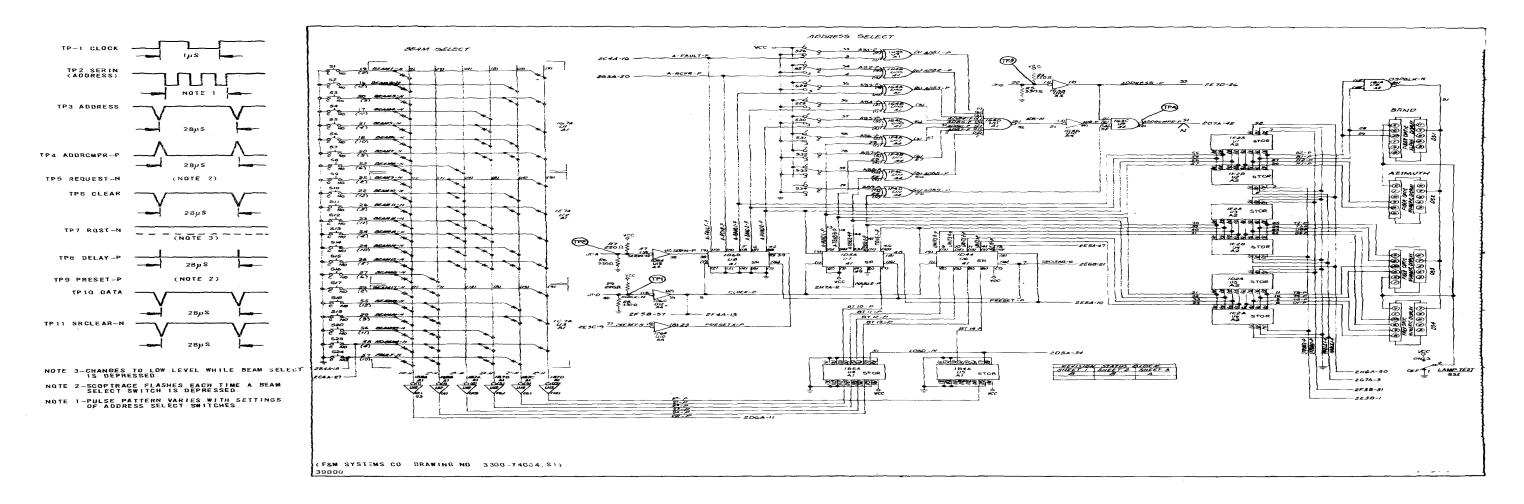

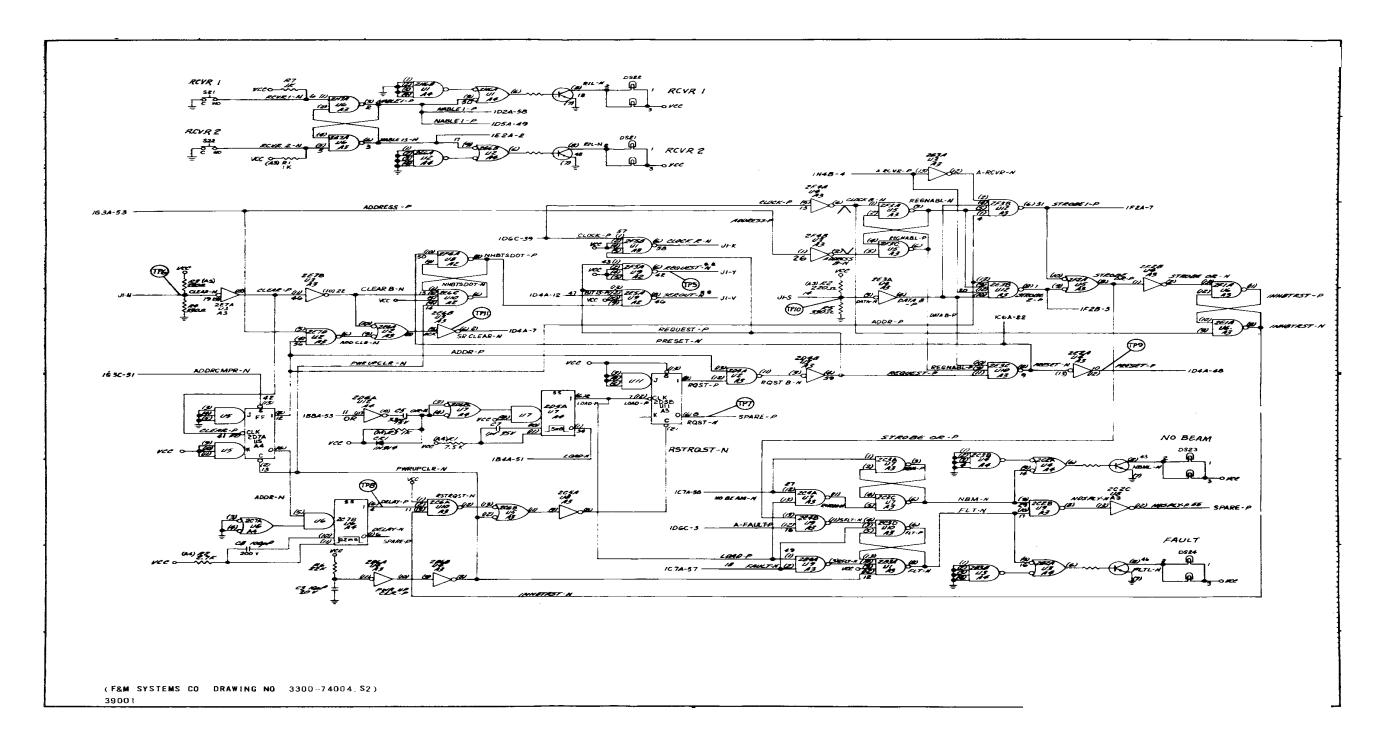

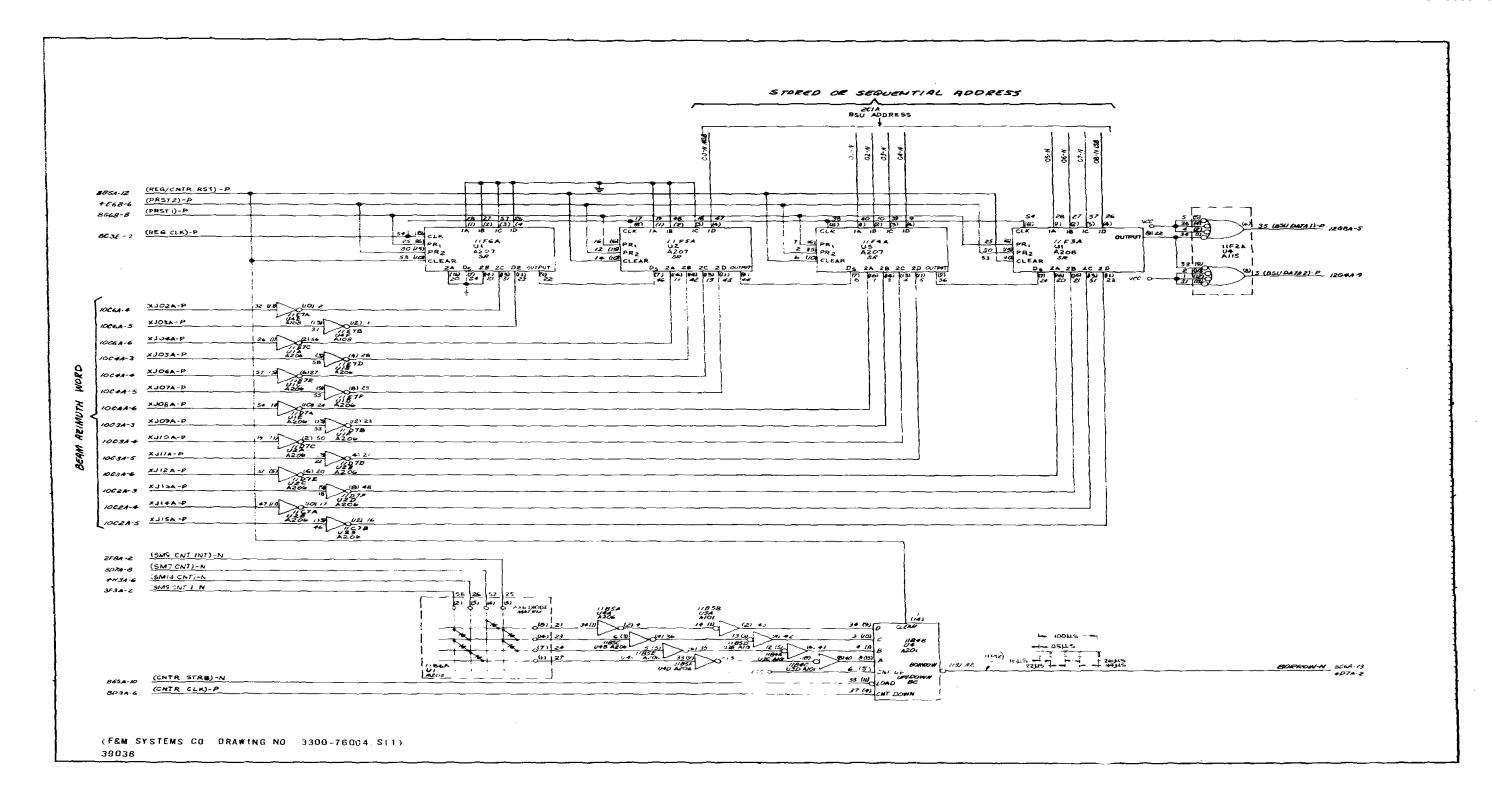

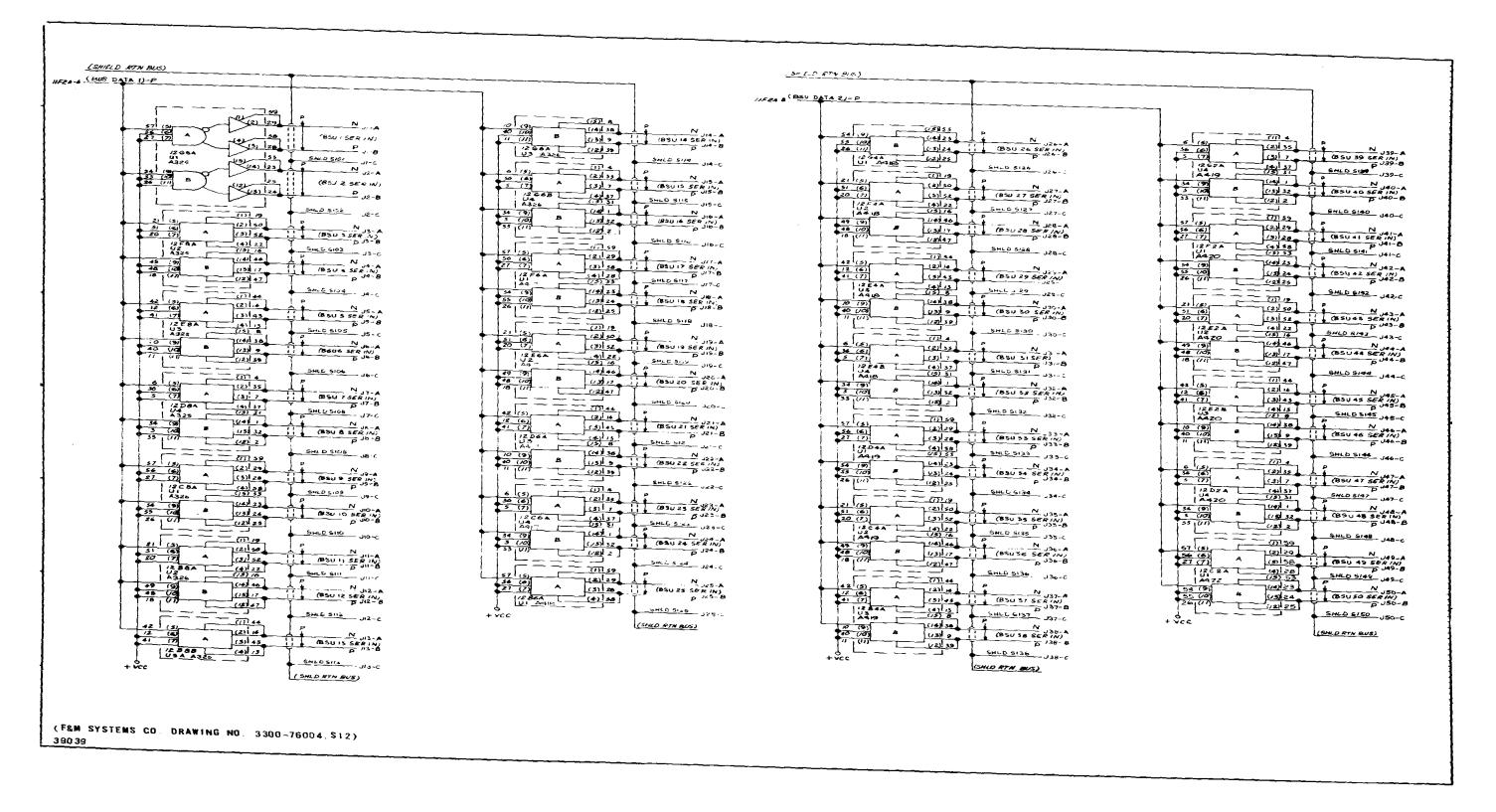

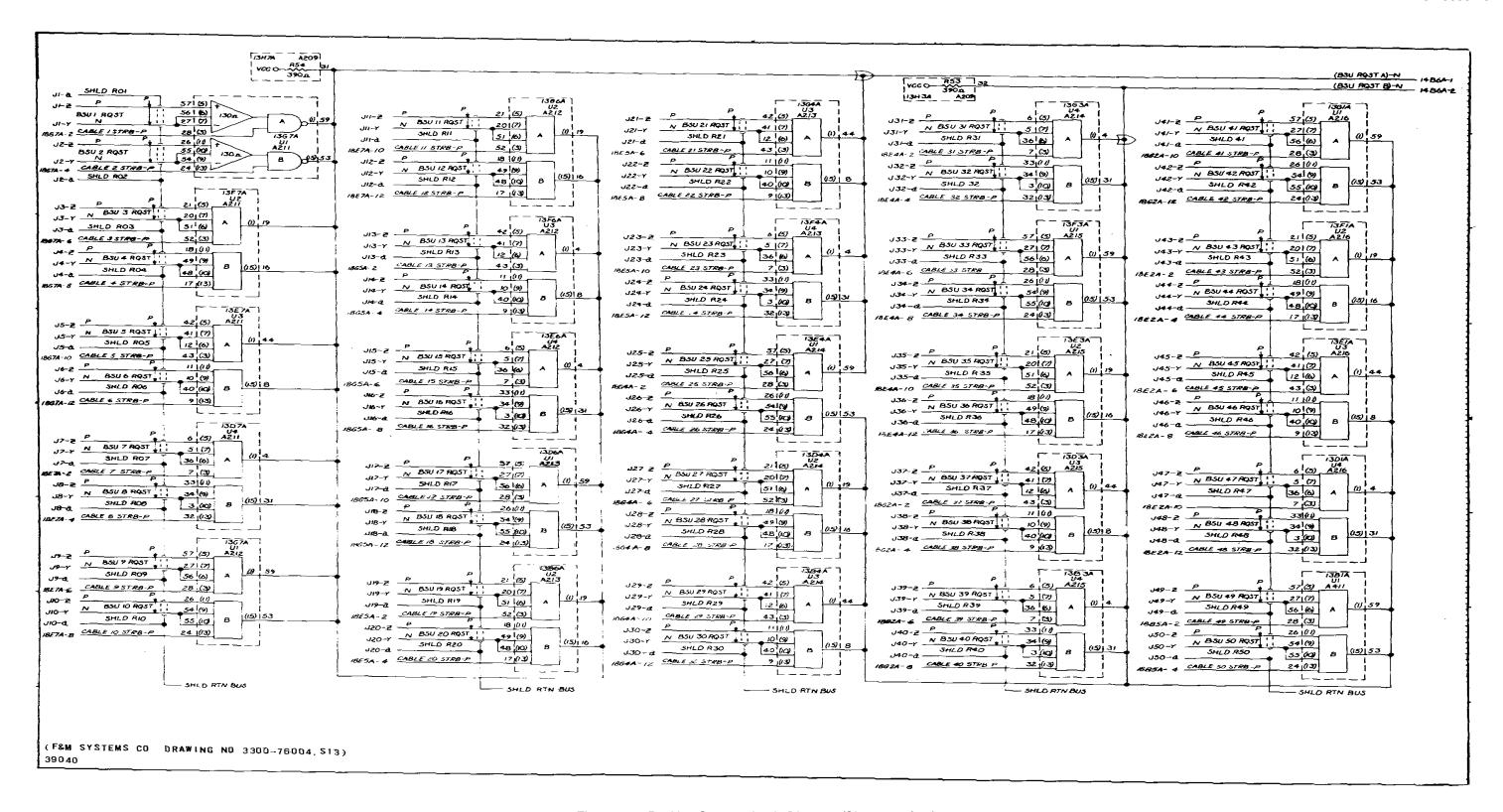

| VII.    | MAIN                                                                                                                                 | TENANCE ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-1                                                                                                                                 |

|         | 7-1.<br>7-2.                                                                                                                         | Scope<br>Logic Circuit Diagram Labeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-1<br>7-1                                                                                                                          |

|         |                                                                                                                                      | GLOSSARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                     |

|         |                                                                                                                                      | INDEX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                     |

|         |                                                                                                                                      | VOLUME 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                     |

| VIII.   | PART                                                                                                                                 | S LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8-1                                                                                                                                 |

|         | 8-1.<br>8-2.                                                                                                                         | Scope Parts List Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-1<br>8-1                                                                                                                          |

| IX.     | WIRE                                                                                                                                 | - CABLE LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9-1                                                                                                                                 |

## LIST OF ILLUSTRATIONS

| Number                                                                                                                                                                                 | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

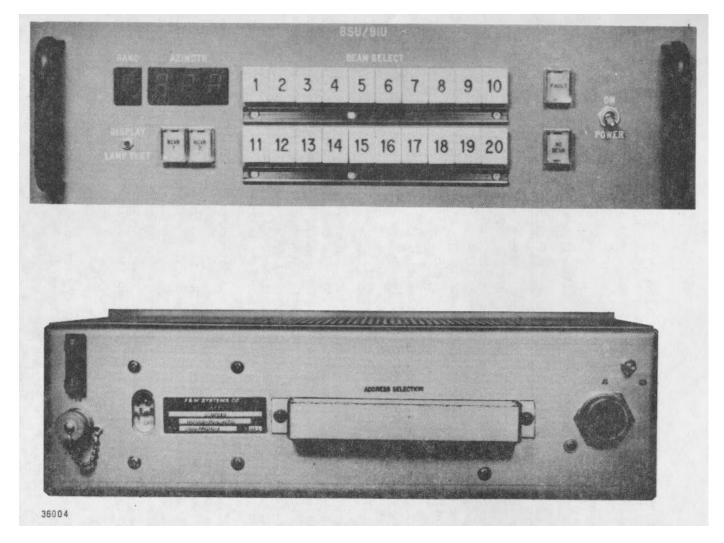

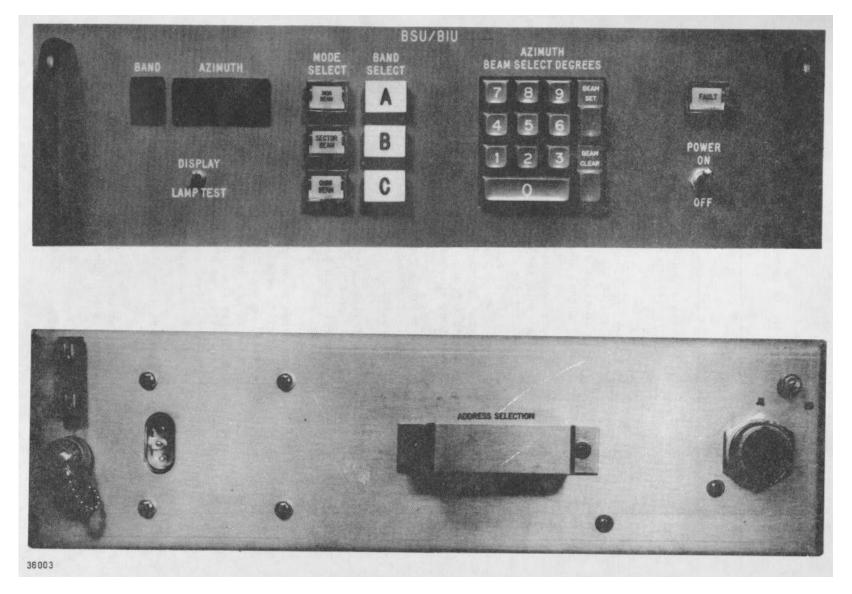

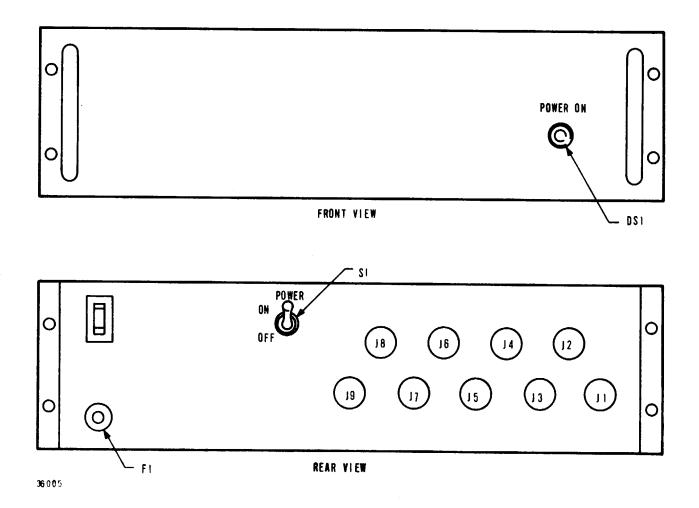

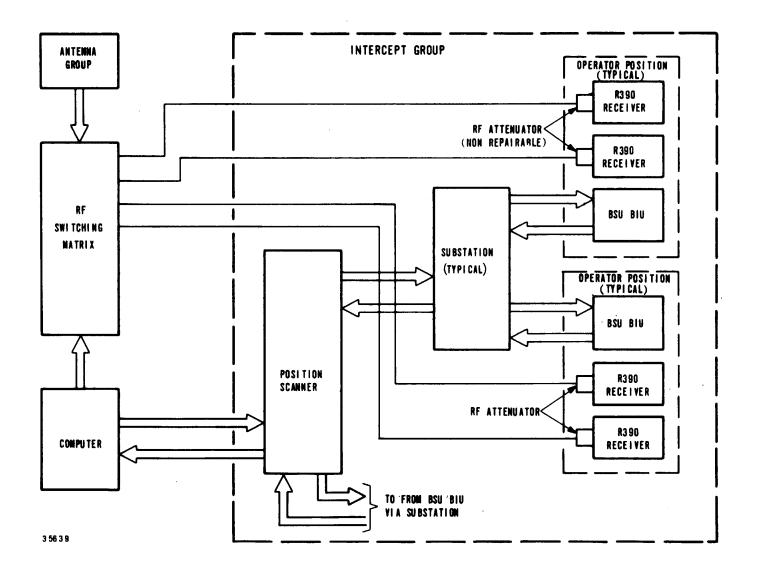

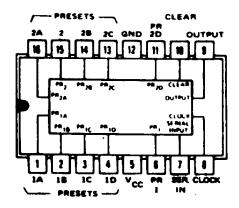

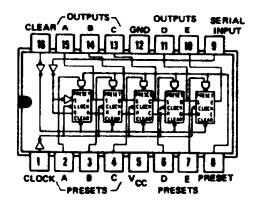

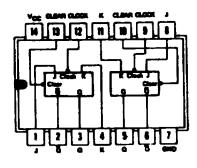

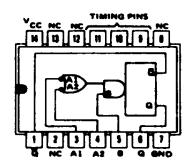

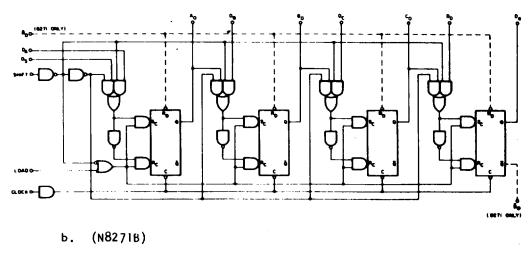

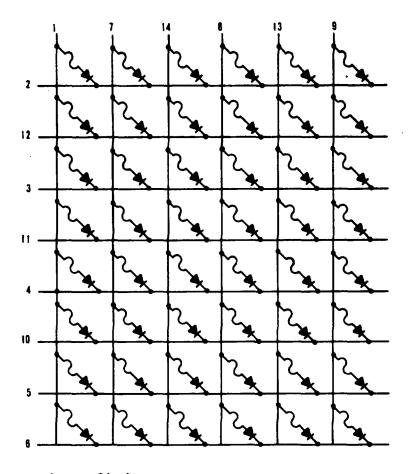

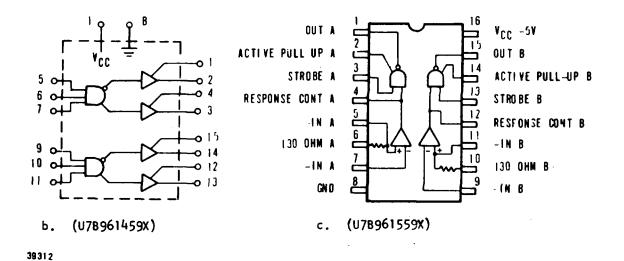

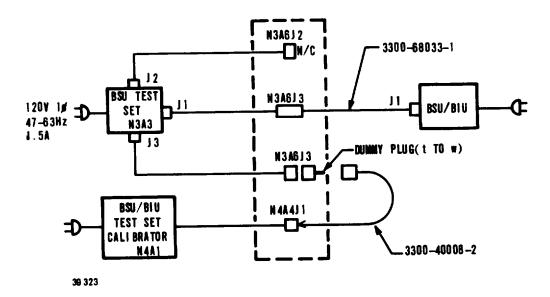

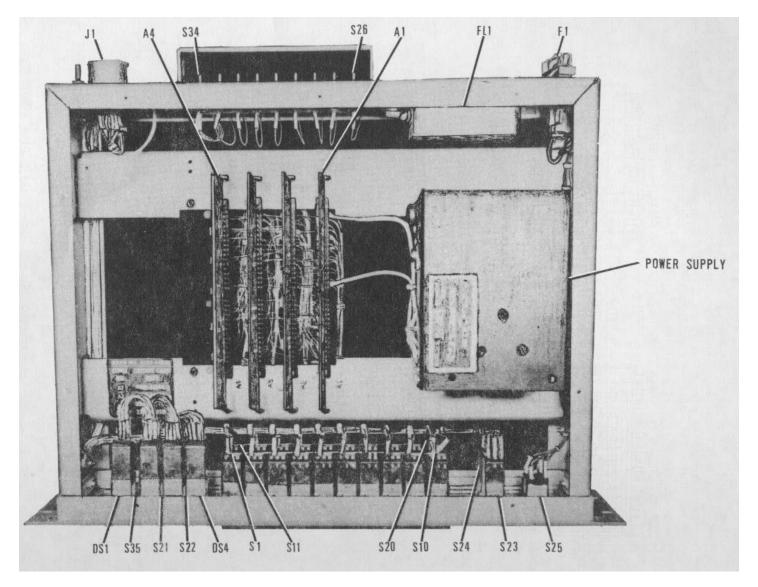

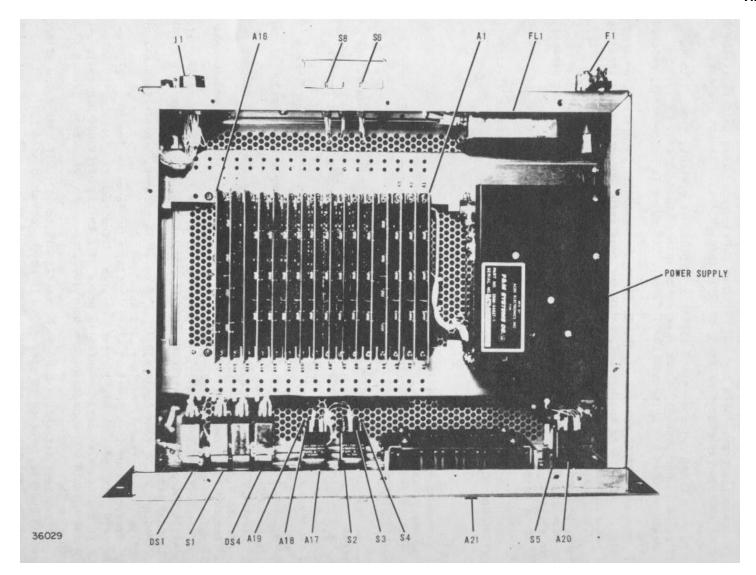

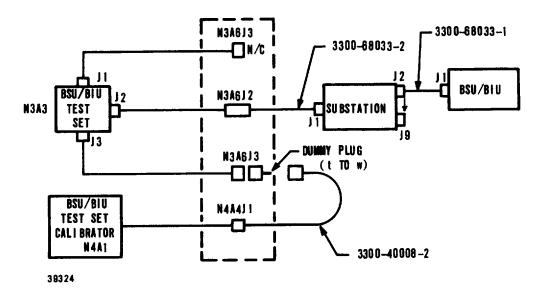

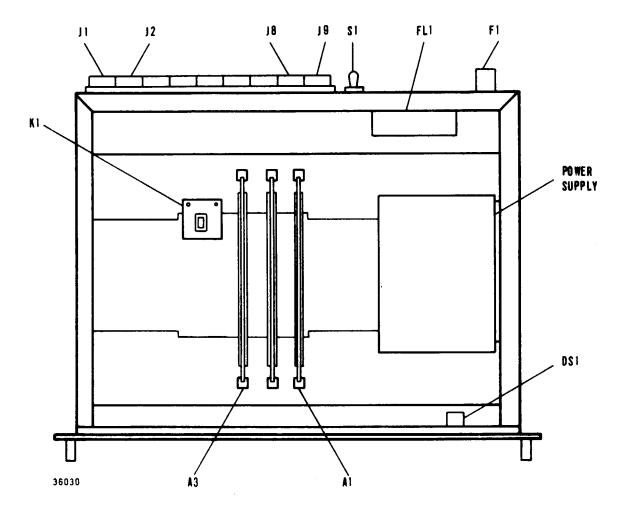

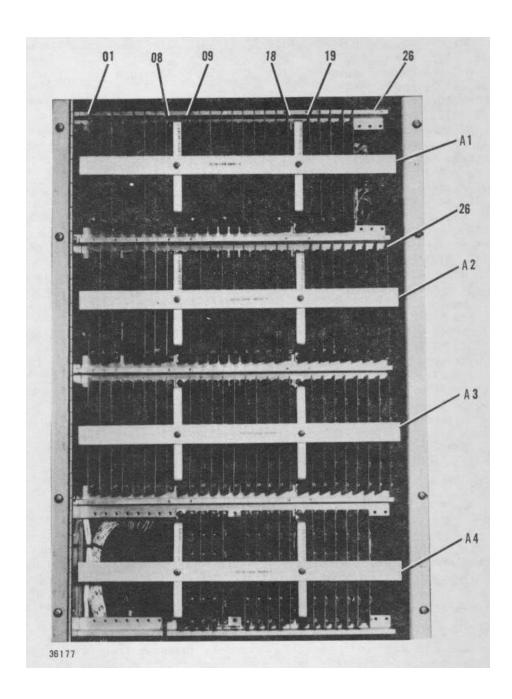

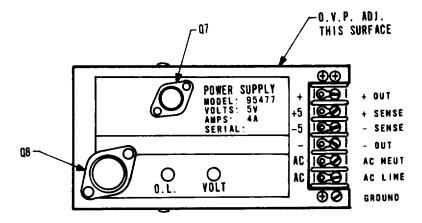

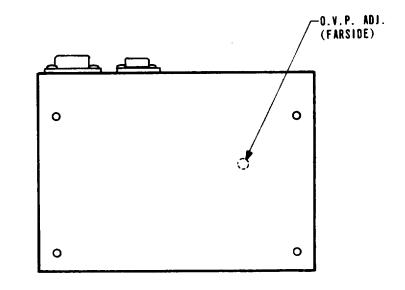

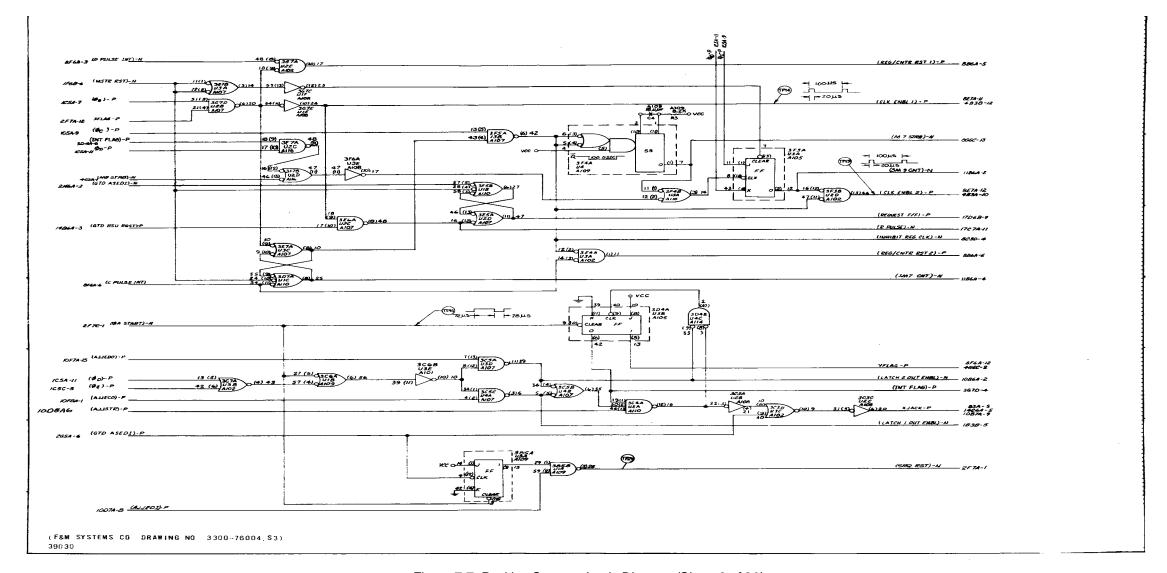

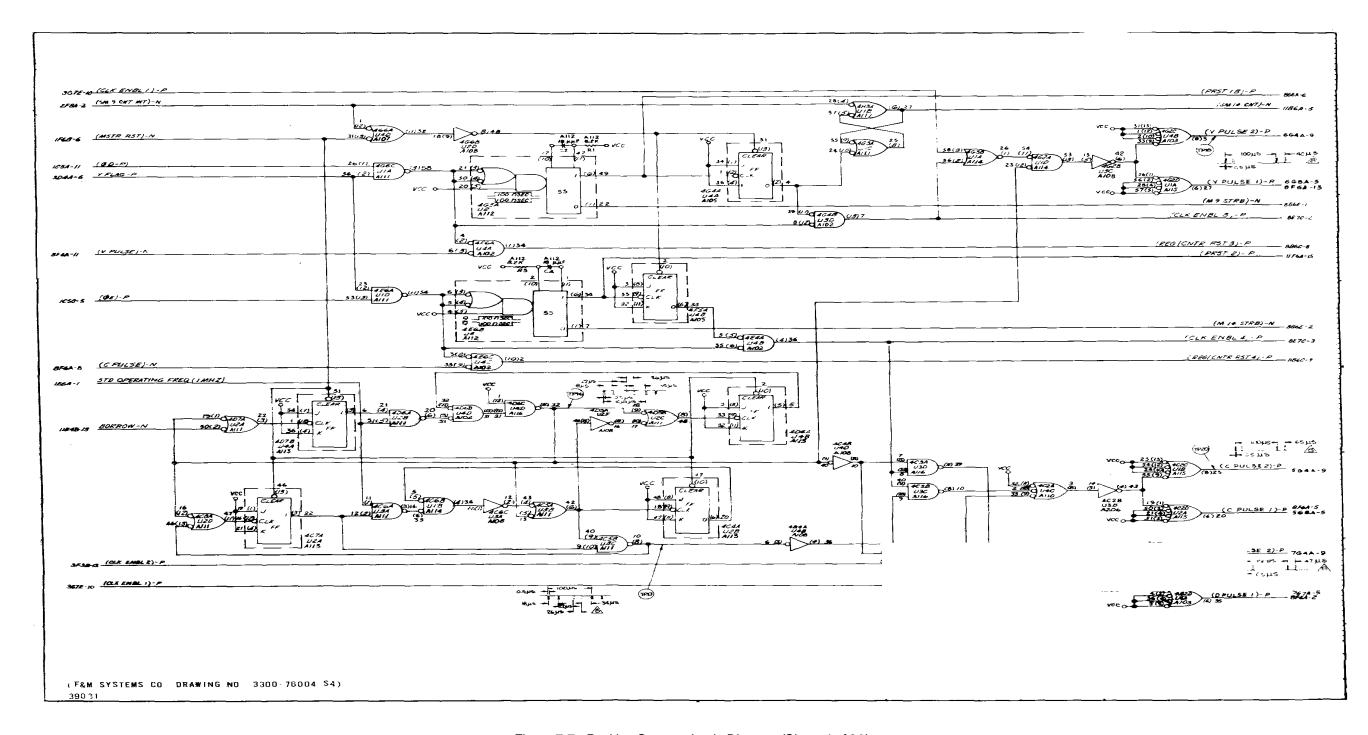

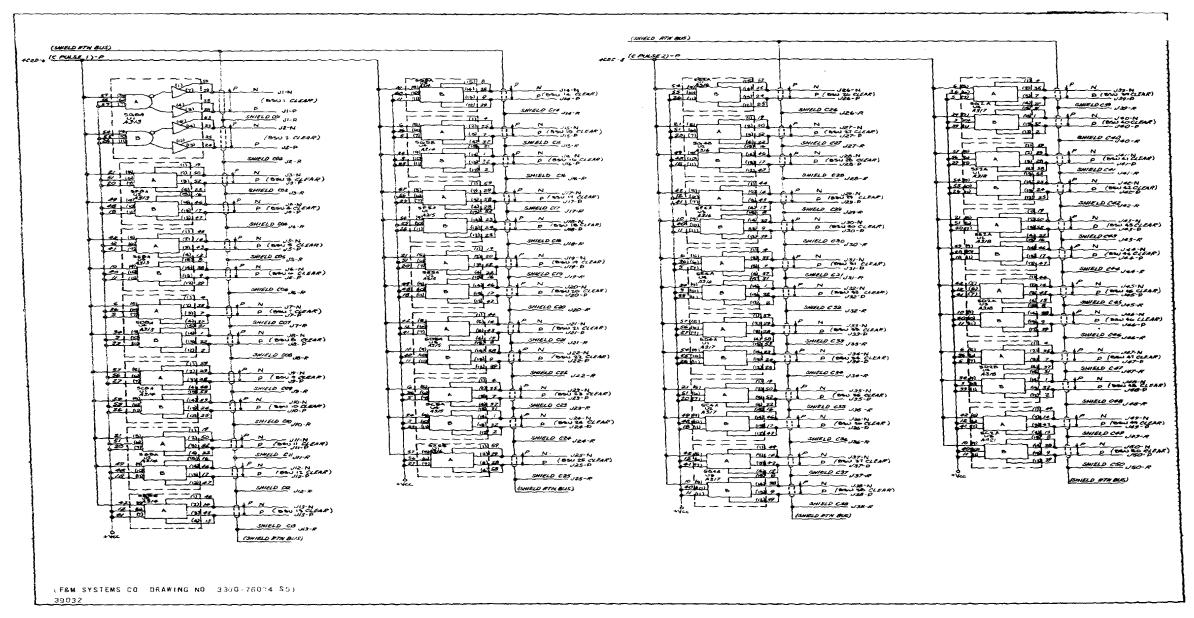

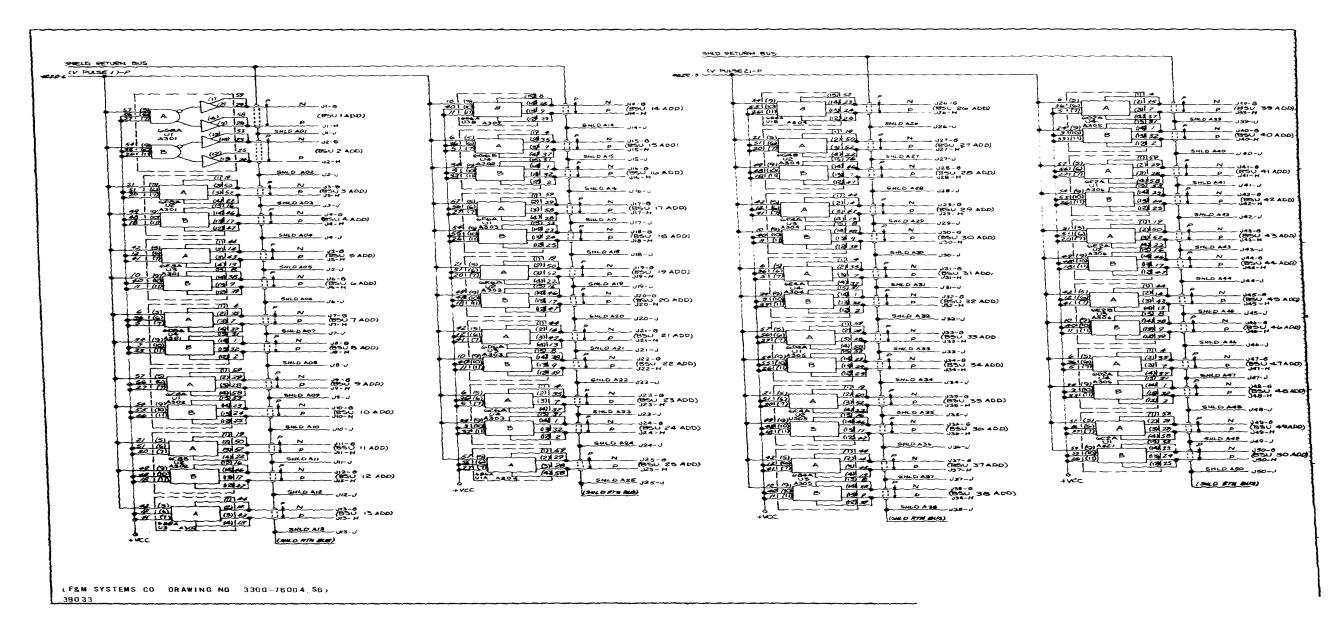

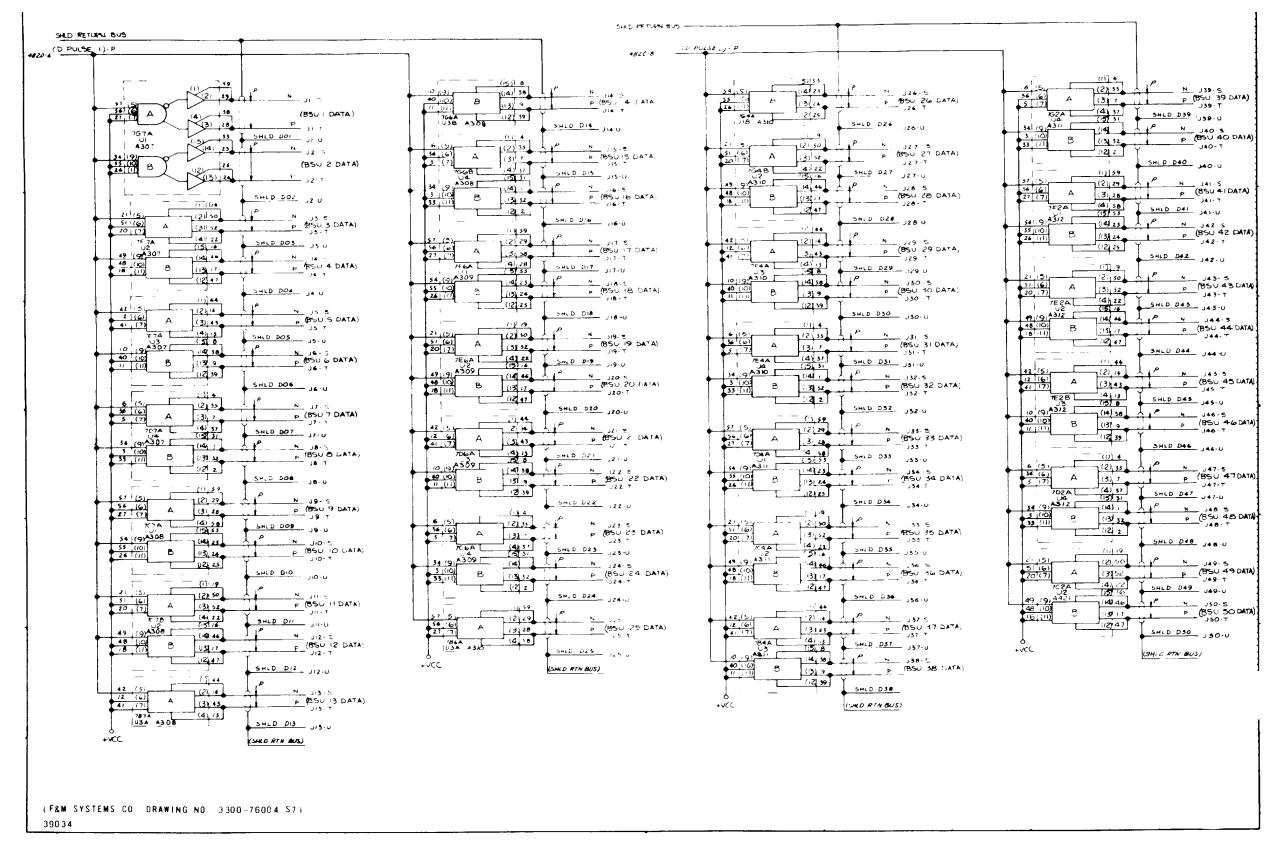

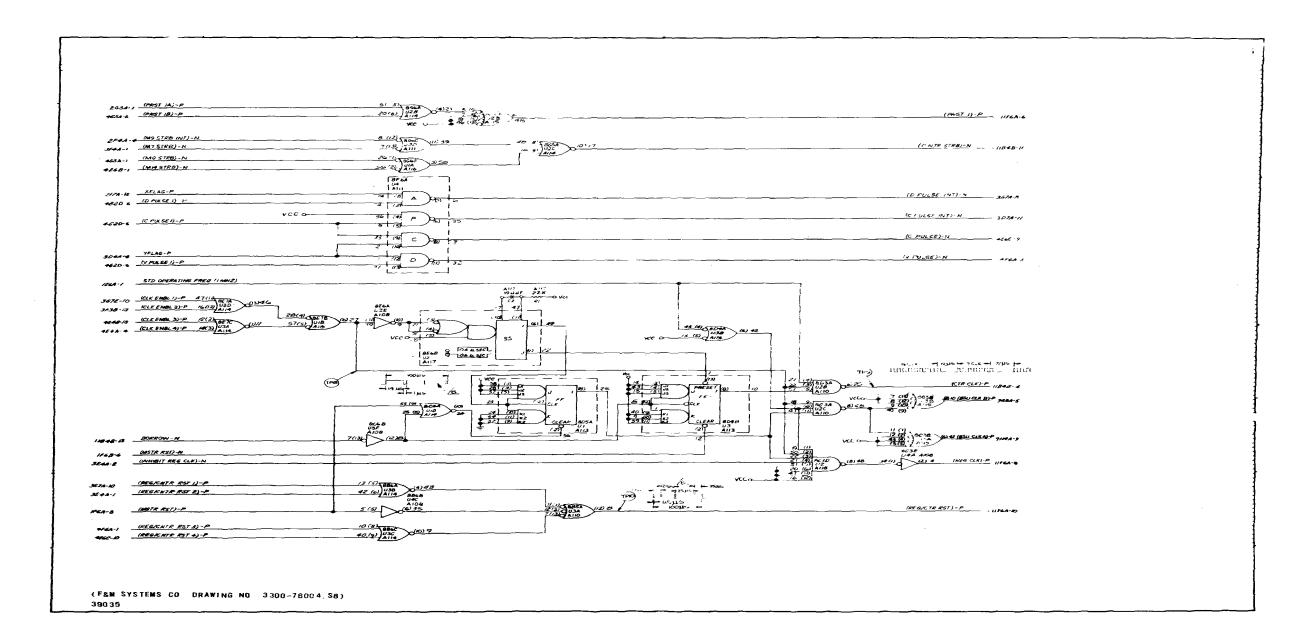

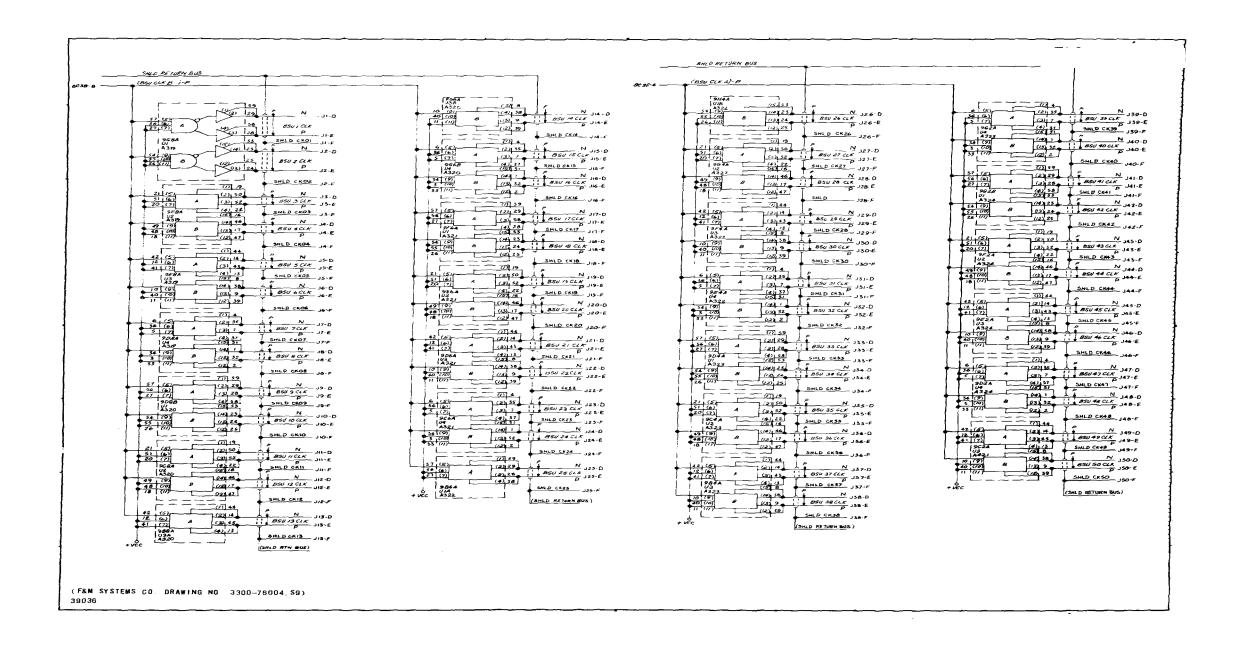

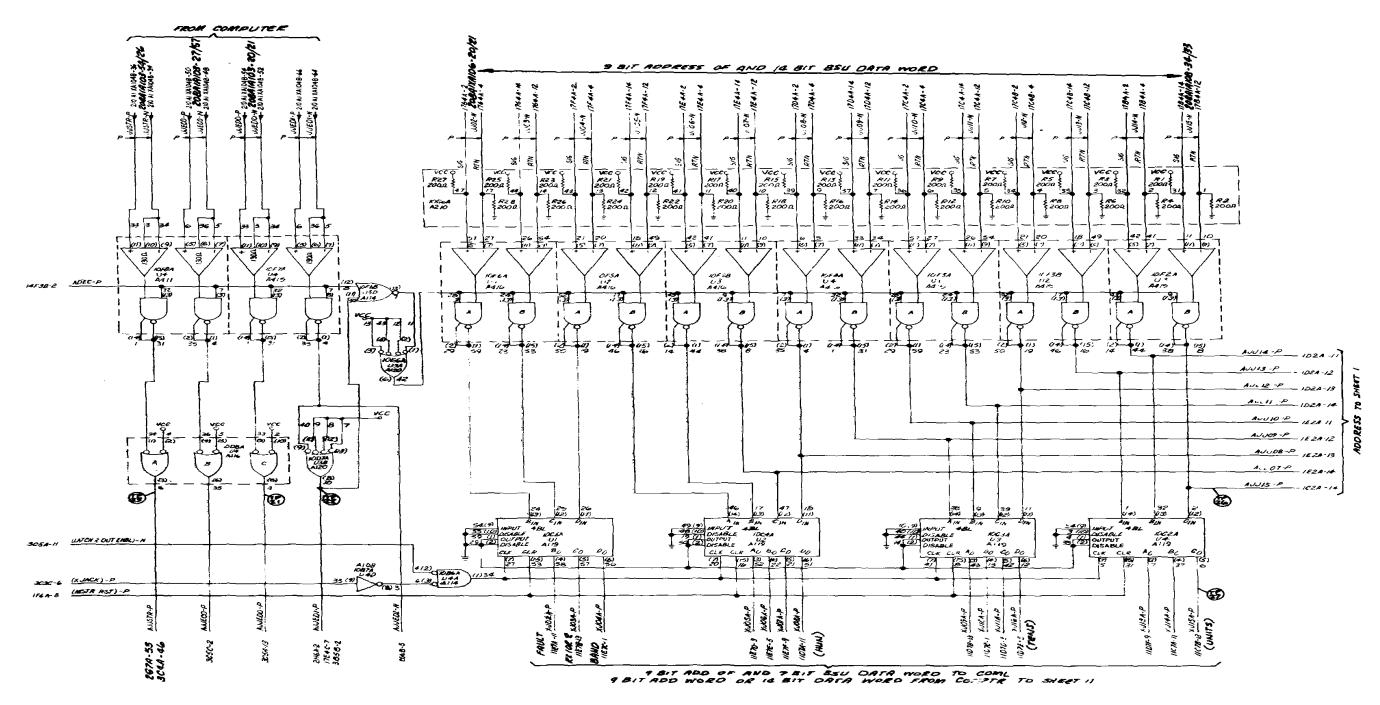

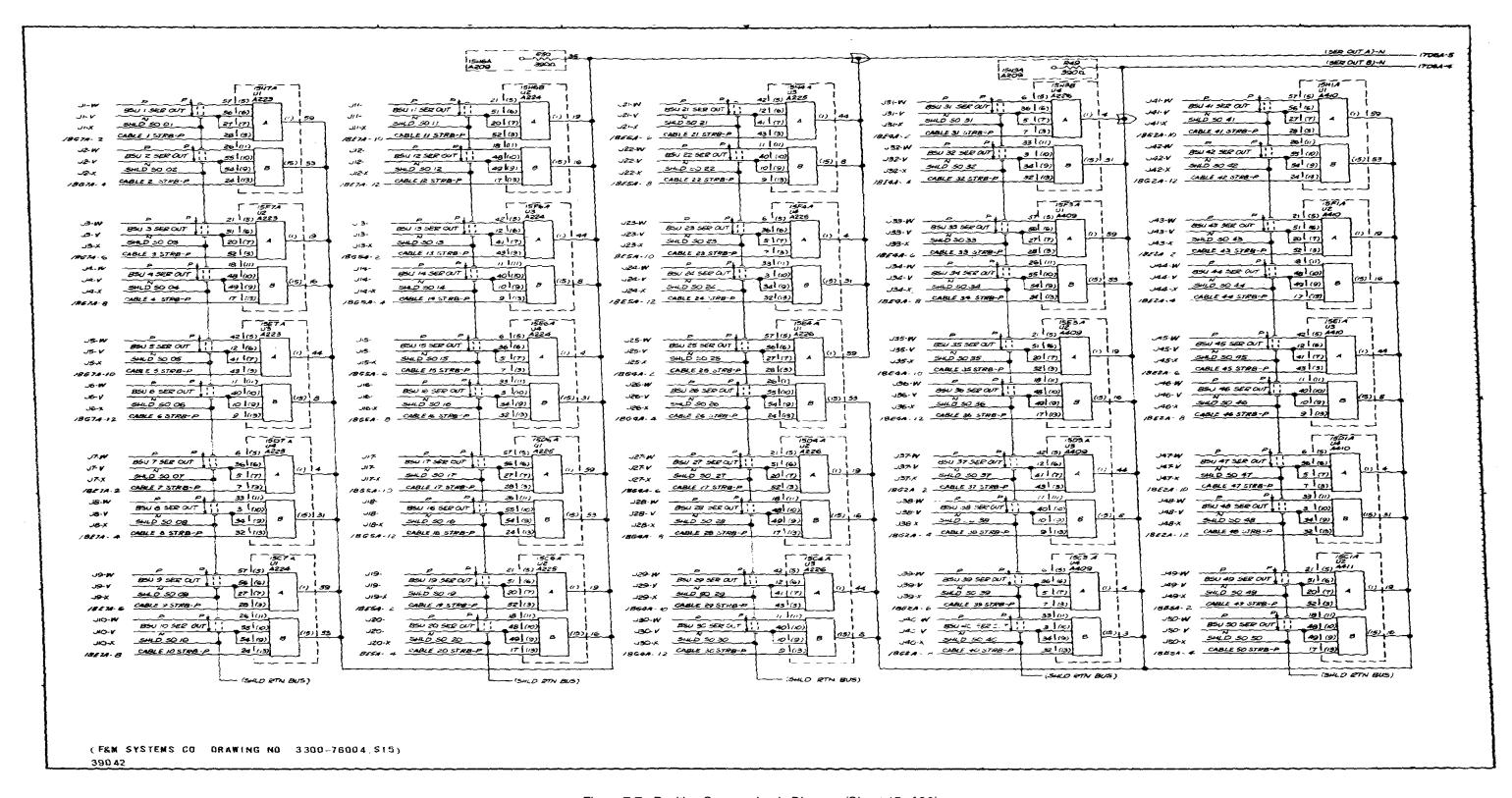

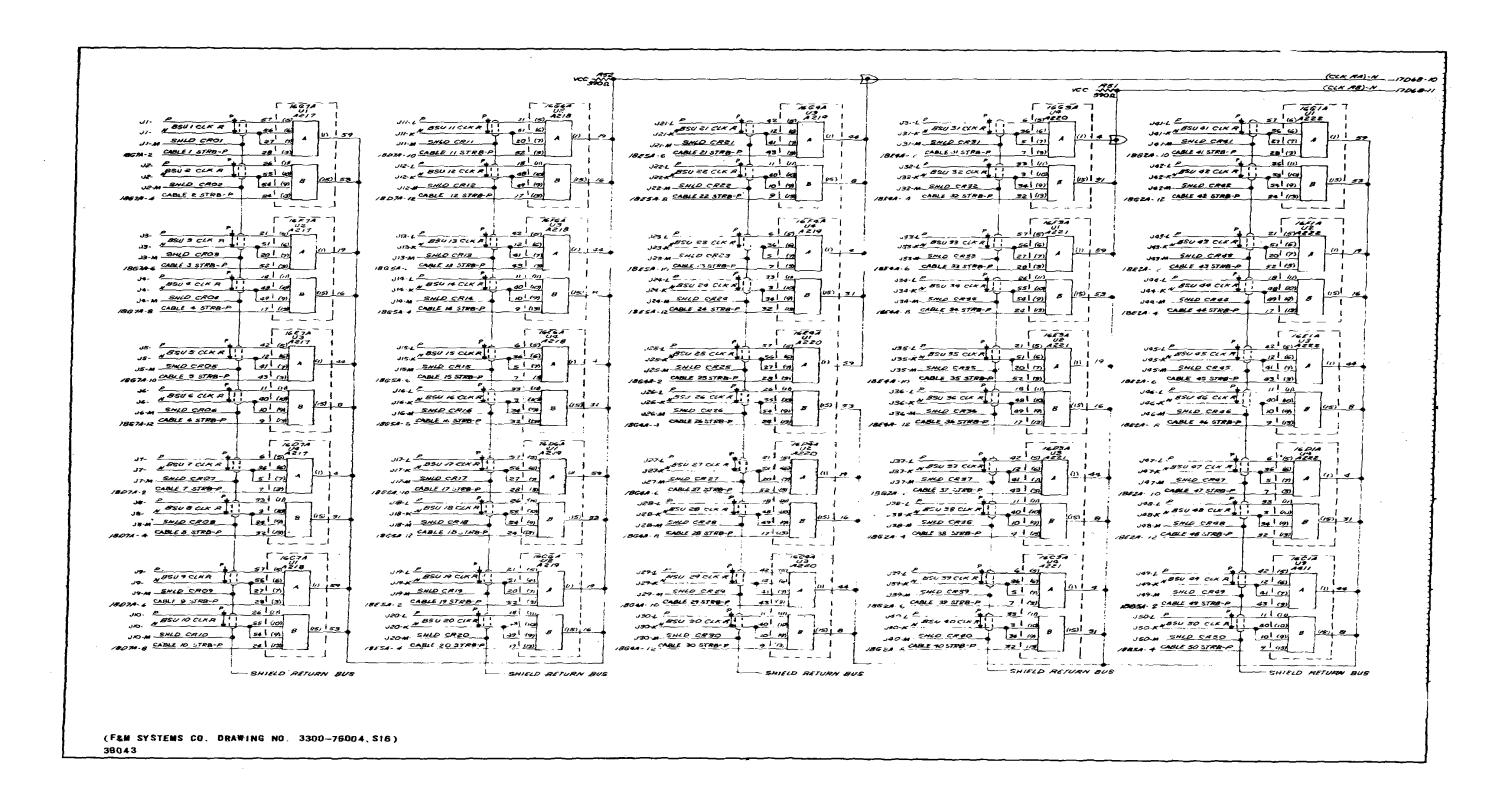

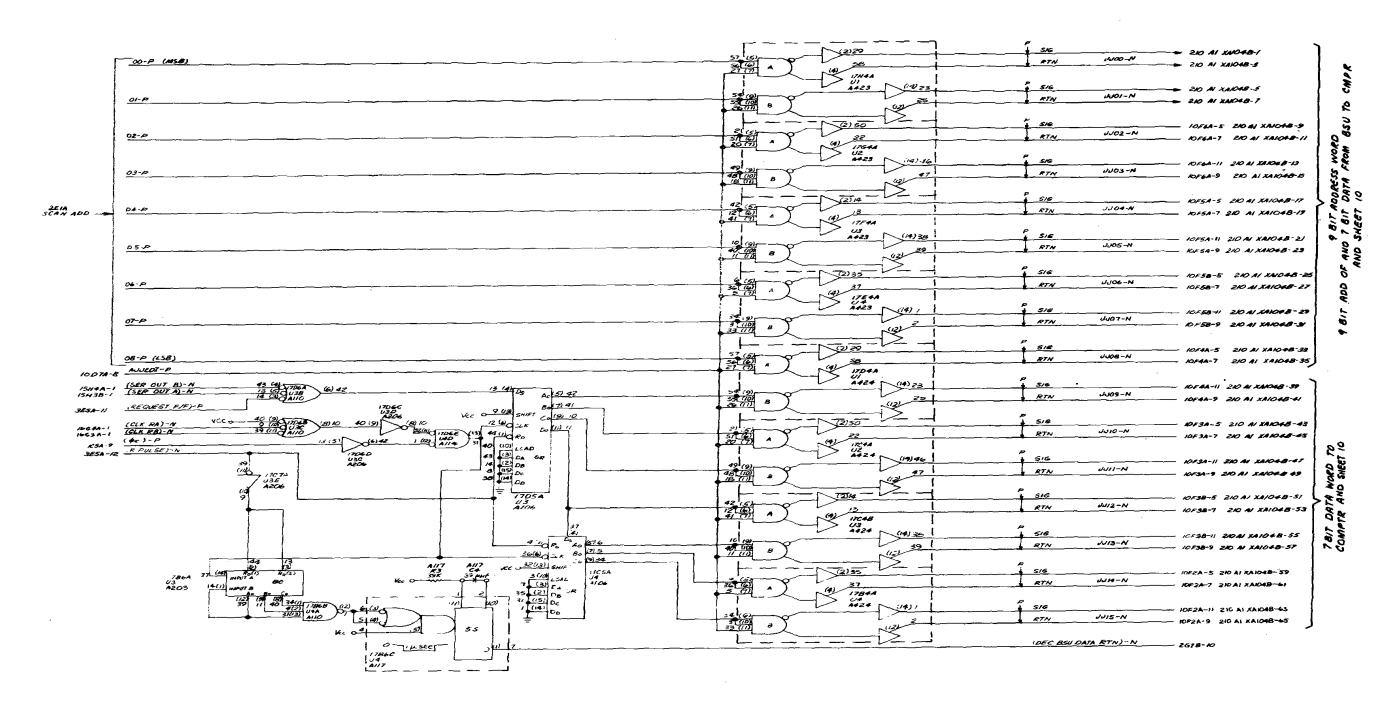

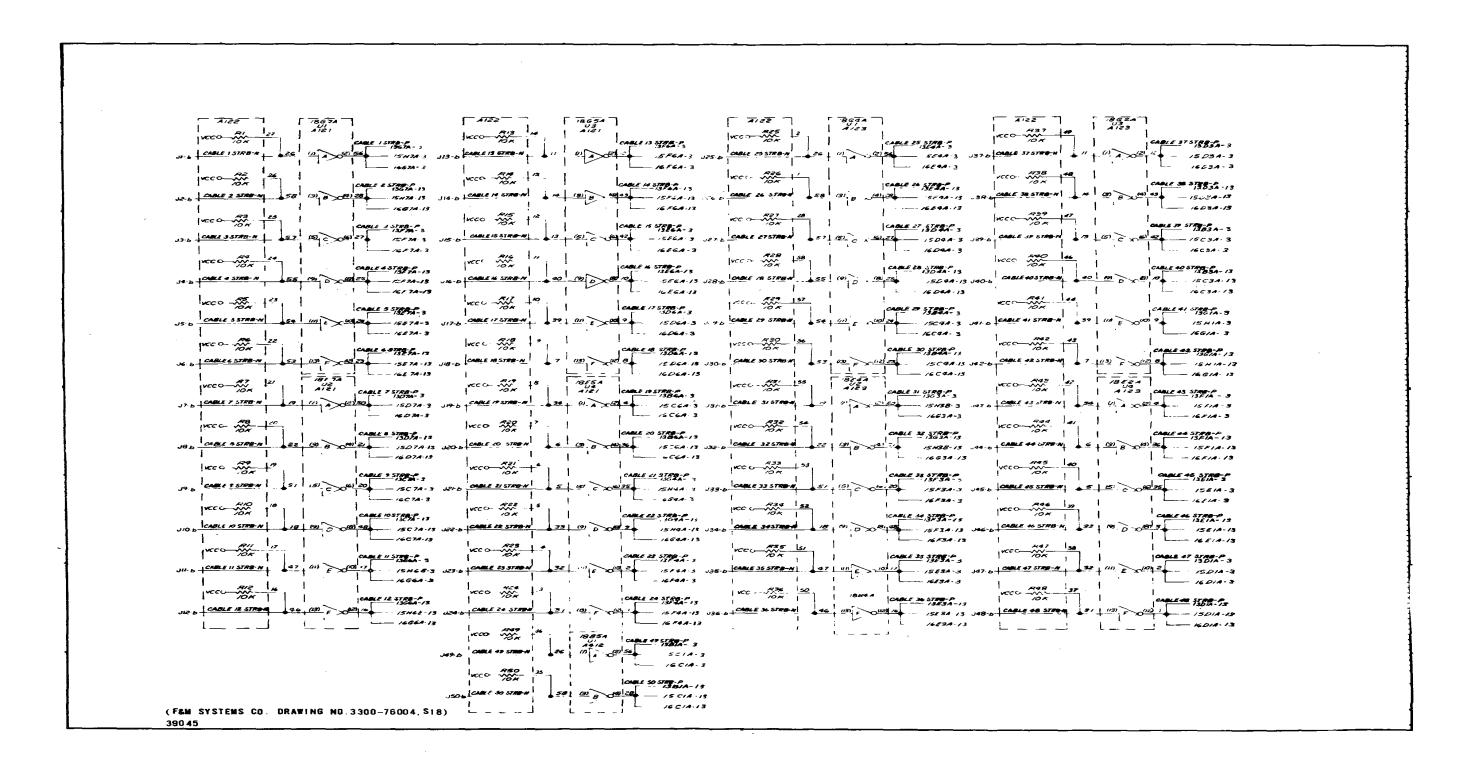

| Number 1-1. 1-2. 2-1. 2-1a. 3-1. 3-2. 3-3. 4-1. 4-2. 4-3. 4-4. 4-5. 4-6. 4-7. 4-8. 4-9. 4-10. 4-11. 4-12. 4-13. 4-14. 5-1. 5-2. 5-3. 5-4. 5-5. 5-6. 5-7. 5-8. 5-9. 7-1. 7-2. 7-3. 7-6. | Intercept Group Typical Equipment Location Intercept Group Equipment Typical Installation Intercept Group Equipment Test Installation Intercept Group Equipment Test Installation Bsu/Biu, Controls and Indicators Special Project Bsu/Biu, Controls and Indicators Substation Operating Controls Intercept Group Block Diagram Intercept Group Simplified Block Diagram Bsu/Biu Block Diagram Special Project Bsu/Biu Block Diagram Special Project Bsu/Biu Block Diagram Substation Block Diagram Power Supply PP-6813/FLR-9(V) Block Diagram Integrated Circuit Connections (SN7400 through SN7430) Integrated Circuit Connections (SN7440 through SN7493) Integrated Circuit Connections (SN7440 through SN74193) Integrated Circuit Connections (SN7494 through SN74193) Integrated Circuit Connections (MC4024P and MC840P) Integrated Circuit Connections (MM017CN and N8271B) Integrated Circuit Connections (RMI-0186-5, U7B961459X, and U78961559X Bsu/Biu Parts Location Special Projects Bsu/Biu Parts Location Substation Test Setup Substation Parts Location Position Scanner 209A1 Parts Location Power Supply Test Setup Power Distribution, Bsu/Biu and Special Project Bsu/Biu Power Distribution, Position Scanner and Substation Bsu/Biu Logic Diagram Special Projects Bsu/Biu Logic Diagram Substation Inhibit Circuit Modification | 1-2<br>1-30<br>2-3<br>2-4a/2-4b<br>3-2<br>3-4<br>3-7<br>4-2<br>4-3<br>4-5<br>4-13<br>4-18<br>4-21<br>4-27<br>4-40<br>4-41<br>4-43<br>4-45<br>4-46<br>4-48<br>4-49<br>5-7<br>5-8<br>5-13<br>5-17<br>5-18<br>5-13<br>5-17<br>5-18<br>5-23<br>5-26<br>5-29<br>5-31<br>7-2<br>7-3<br>7-4<br>7-5<br>7-13<br>7-21 |

| 7-6.<br>7-7.<br>7-8.<br>9-1.                                                                                                                                                           | Position Scanner Logic Diagram Power Supply PP-6813/FLR-9(V) Schematic Diagram Intercept Group, Cabling Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-21<br>7-23<br>7-63<br>9-2                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                        | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                             |

| Number                                                                                                                                                                                 | Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                                                                                                                                                                                                                                                        |

| Number | Number                              | Page |

|--------|-------------------------------------|------|

| 1-1.   | Leading Particulars                 | 1-3  |

| 1-2.   | Capabilities and Limitations        | 1-4  |

| 1-3.   | Equipment Supplied                  | 1-4  |

| 1-4.   | Equipment Required But Not Supplied | 1-5  |

Change 2 iii

# TM 32-5895-234-15

# LIST OF TABLES (Continued)

| Number | Title                                                  | Page |

|--------|--------------------------------------------------------|------|

| 1-5.   | AN/FLR-9(V7) Reference Designators and Bsu/Biu Address | 1-6  |

| 1-6.   | AN/FLR-9(V8) Reference Designators and Bsu/Biu Address | 1-14 |

| 1-7.   | List of Publications                                   | 1-31 |

| 2-1.   | Inspection                                             | 2-1  |

| 3-1.   | Bsu/Biu Controls and Indicators                        | 3-3  |

| 3-2.   | Special Project Bsu/Biu Controls and Indicators        | 3-5  |

| 3-3.   | Substation Controls and Indicators                     | 3-8  |

| 4-1.   | Bsu/Biu Circuit Cards                                  | 4-29 |

| 4-2.   | Special Project Bsu/Biu Circuit Cards                  | 4-29 |

| 4-3.   | Bsu/Biu Substation Circuit Cards                       | 4-29 |

| 4-4.   | Position Scanner Circuit Cards                         | 4-30 |

| 4-5.   | Intercept Group Integrated Circuit Complement          | 4-31 |

| 5-1.   | Maintenance Schedule                                   | 5-1  |

| 5-2.   | Test Equipment Required                                | 5-2  |

| 5-3.   | Bsu/Biu Troubleshooting                                | 5-11 |

| 5-4.   | Special Project Bsu/Biu Troubleshooting                | 5-15 |

| 5-5.   | Substation Troubleshooting                             | 5-19 |

| 5-6.   | Position Scanner Troubleshooting                       | 5-20 |

| 5-7.   | Power Supply Troubleshooting                           | 5-27 |

| 5-8.   | Minimum Performance Standards                          | 5-32 |

| 6-1.   | Inspection Standard Tests                              | 6-1  |

| 9-1.   | Wire/Cable List Cross Reference Index                  | 9-1  |

#### **SECTION I**

#### **DESCRIPTION**

### 1-1. Scope of Manual.

This two volume manual contains installation operation, theory of operation, maintenance, and depot inspection standards for the Intercept Group AN/FLR-9(V7) and (V8) and newly designed equipments contained therein. The two configurations, AN/FLR-9(V7) and AN/FLR-9(V8), differ only in the number of equipments used. These equipments include Selector, Beam SA-1870/FLR-9(V) (bsu/biu); Selector, Beam SA-1871/FLR-9(V) (special project bsu/biu); the substation (3300-44019); and the position scanner (3300-46030). Each of these equipments is described in detail within the manual. Unless otherwise specified, descriptions of the bsu/biu also apply to the special project bsu/biu. In addition, a power supply common to each equipment is described. Publications describing support equipments used in the intercept group are listed in paragraph 1-10. Volume 1 contains maintenance description, volume 2 contains parts and wire lists.

### **1-2. Purpose of Manual.** (See figure 1-1.)

This manual describes the Intercept Group associated with Countermeasures Receiving Set AN/FLR-9(V7)/(V8). The manual covers installation, operation, theory of operation maintenance, and depot inspection standards. Maintenance includes cleaning, inspecting, parts replacement, troubleshooting, alignment and repair for the operation and unit repairman. Depot inspection standards include a list of test equipment, tools, and special appliances required to perform associated optimum performance standards tests.

### 1-3. Description and Purpose.

#### a. Description.

- 1. <u>Bsu/biu</u>. The intercept group bsu/biu provides each mission operator with the capability of selecting any 1 of 20 antenna beams for each of 2 associated receivers at the V7 site and 20 beams for both receivers at the V8 site. Selected antenna beams provided rf signals to the receivers on one of three bands (2 MHz to 6 MHz, 6 MHz to 18 MHz, 18 MHz to 30 MHz) In selected azimuthal direction. The band and azimuth selected for each receiver is displayed at the user operator position bsu/biu.

- 2. <u>Special Project Bsu/Biu</u>. The intercept group special project bsu/biu provides certain operators with the capability of selecting all possible antenna azimuth angles, types of beams, and frequency band for a single receiver. The special project bsu/biu indicates the selected band, beam, and azimuth when the connections have been made.

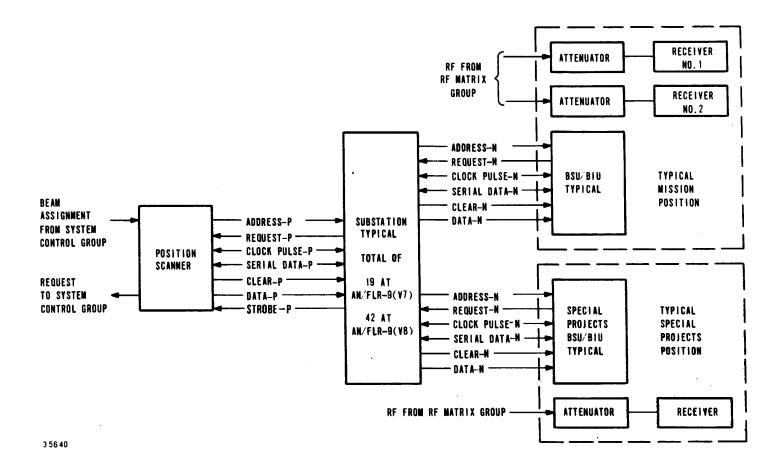

- 3. <u>Substation</u>. Each intercept group substation provides interface between each bsu/biu and the position scanner. This interface amounts to line impedance matching and driving.

- 4. <u>Position Scanner</u>. The intercept group position scanner provides control and data to all bsu/biu and special project bsu/biu, as supplied by the system

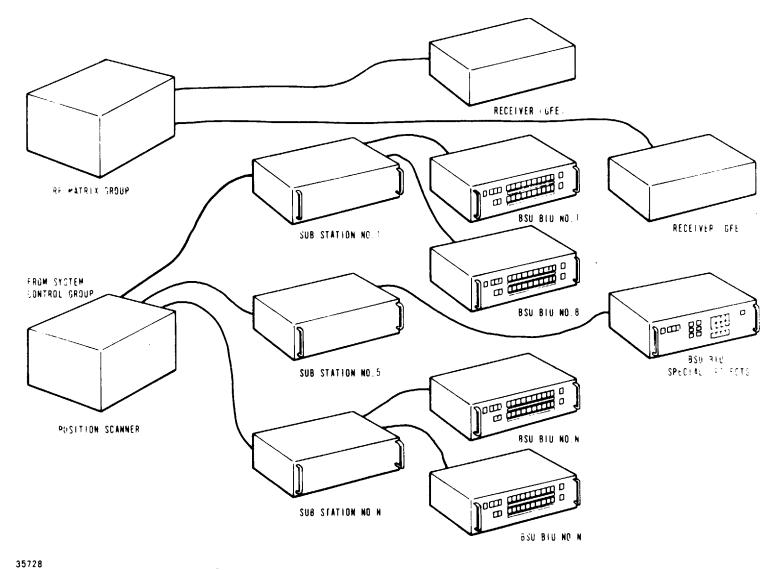

Figure 1-1. Intercept Group

control group. This interfacing includes timing, data and address recognition, and service request recognition.

#### b. Purpose.

- 1. Intercept group equipment consists of a bsu/biu at each mission operator position. The mission operator selects pre-programmed antenna beams by momentarily pressing 1 of the 20 BEAM SELECT switches and 1 of 2 receiver switches on the bsu/ biu. The antenna beam request calls up a computer program routine in the system control group computer which identifies the azimuth and rf band associated with the BEAM SELECT switch. Switchpoint closure signals are provided for the switch matrix to select the requested rf signal. The rf signal is coupled directly to the selected receiver while a switch closure verification signal is supplied to the system control group computer. This signal is converted to a BCD signal and returned to the bsu/biu as the azimuth and rf band signal. These signals provide a visual readout of the azimuth and band in use. The special project bsu/biu purpose is the same except that all beam azimuth angles are available.

- 2. Interface between the bsu/biu and the system control group is provided by a substation and the position scanner. The substation provides signal distribution which allows eight bsu/biu to interface with the position scanner on one input/output line. The position scanner provides proper interface to the computer.

- 1-4. Leading Particulars. (See table 1-1.)

Leading particulars are listed in table 1-1.

Table 1-1. Leading Particulars

|                                                                | Power                                                       | Dir          | Dimensions in Inches |       |      |  |

|----------------------------------------------------------------|-------------------------------------------------------------|--------------|----------------------|-------|------|--|

| ltem                                                           | Requirements                                                | Height Width |                      | Depth | (lb) |  |

| Selector,<br>Beam SA-1870<br>FLR-9(V)<br>(Bsu/biu)             | 120 ±12 volts<br>47 to 63 Hz<br>single-phase<br>0.5 ampere  | 5.2          | 19                   | 13.5  | 18   |  |

| Selector,<br>Beam SA-1871<br>FLR-9(V)(Special Project bsu/biu) | 120 ± 12 volts<br>47 to 63 Hz<br>single-phase<br>0.5 ampere | 5.2          | 19                   | 13.5  | 19   |  |

| Substation<br>3300-44019-1                                     | 120 ± 12 volts<br>47 to 63 Hz<br>single-phase<br>0.5 ampere | 5.2          | 9                    | 13.5  | 7    |  |

| Position<br>Scanner<br>3300-46030-1                            | 5 volts dc<br>20 amperes                                    | 28           | 19                   | 6     | 12   |  |

# 1-5. Capabilities and Limitations. (See table 1-2.)

Capabilities and limitations are listed in table 1-2.

Table 1-2. Capabilities and Limitations

| Characteristic                                          | Limits                                                                  |

|---------------------------------------------------------|-------------------------------------------------------------------------|

| Signal Level (All Units) Positive logic used throughout | +5 volts dc                                                             |

| Binary levels<br>High                                   | +5 volts dc                                                             |

| Low                                                     | 0 volt dc                                                               |

| Operating Environment (All Units) Temperature Humidity  | 0°C to 50°C<br>Up to 95 percent relative, without condensation          |

| Output signal of bsu/biu<br>Bsu/biu                     | 7-bit serial word to input of position scanner                          |

| Special project bsu/biu                                 | 14-bit serial word to input of position scanner                         |

| Input signal to (either) bsu/biu                        | 14-bit receiver beam assignment word from computer via position scanner |

|                                                         | 9-bit address word from position scanner                                |

# 1-6. Equipment Supplied. (See table 1-3.)

Equipment supplied is listed in table 1-3.

Table 1-3. Equipment Supplied

|      |                                                           | Qua          | Quantity     |  |  |

|------|-----------------------------------------------------------|--------------|--------------|--|--|

| Item | Name                                                      | AN/FLR-9(V7) | AN/FLR-9(V8) |  |  |

| 1    | Selector, Beam SA-1870/FLR-9(V) (bsu/biu)                 | 133          | 316          |  |  |

| 2    | Substation 3300-44019-1                                   | 19           | 42           |  |  |

| 3    | Selector, Beam SA-1871/FLR-9(V) (special project bsu/biu) | 3            | 3            |  |  |

Table 1-3. Equipment Supplied (Continued)

| _    | Name                                  | Quantity     |                |  |

|------|---------------------------------------|--------------|----------------|--|

| Item |                                       | AN/FLR-9(V7) | AN/FLR-9(V8)   |  |

| 4    | Position Scanner 3300-46030-1         | 1            | 1              |  |

| 5    | Connector, Rf Attenuator 3300-40025-1 | One for each | <br>h receiver |  |

## 1-7. Equipment Required But Not Supplied. (See table 1-4.)

Equipment required but not supplied with the intercept group is listed in table 1-4.

Table 1-4. Equipment Required But Not Supplied

| Item | Name                                          | Quantity                             |

|------|-----------------------------------------------|--------------------------------------|

| 1    | Radio Receiver R-390A/URR or equivalent (GFE) | Two for each bsu/biu                 |

| 2    | Radio Receiver R-390A/URR or equivalent (GFE) | One for each special project bsu/biu |

#### 1-8. Model Differences.

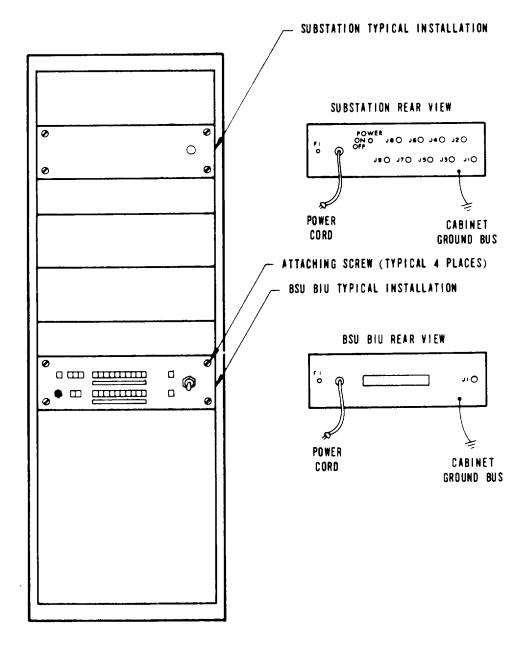

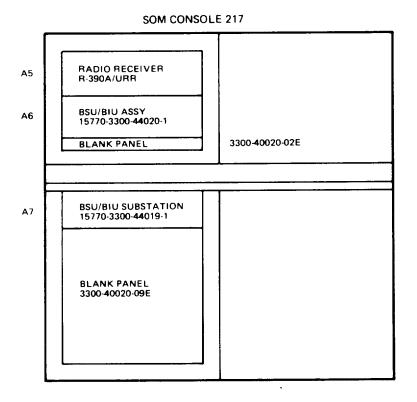

Equipments used in the AN/FLR-9(V7)and (V8) Intercept Groups are identical. The only difference in the two groups is the number of equipments used and the configuration of the SOM Console at V8(see fig 2-1a). For quantity, refer to table 1-3.

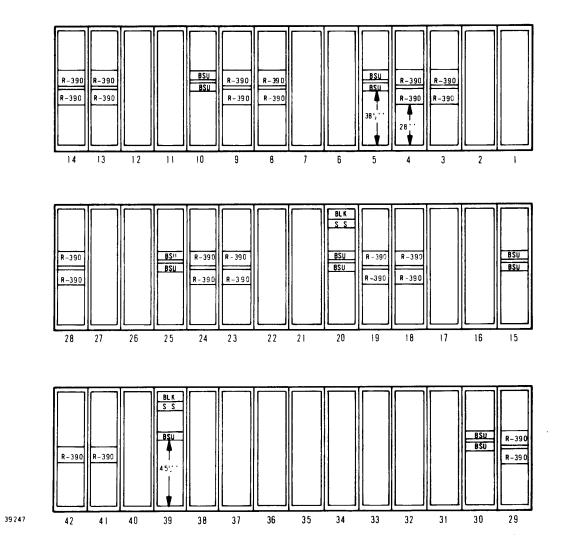

### 1-9. Reference Designation. (See tables 1-5 and 1-6 and figure 1-2.)

One position scanner is used in the intercept group. This unit is located in rack 209 with the system control group equipment. Three special project bsu/biu are used in the AN/FLR-9(V7) and (V8) sites. At the AN/FLR-9(V8) site, 317 bsu/biu are supplied whereas 134 are supplied in the AN/FLR-9(V7) site. In the AN/FLR-9(V8) site, 43 substations are supplied, and 20 are supplied at the AN/FLR-9(V7) site. The preceding units, with the exception of the position scanner, are located at positions determined by the user. The unit locations are listed in tables 1-5 and 1-6 and are typical locations for these units. As many as eight bsu/biu are listed with a substation which is associated with these units. The listing consists of two columns, Row and Rack. The letter U in the Rack column indicates the upper unit, letter L indicates lower unit. Figure 1-2 illustrates a typical row of equipment.

Table 1-5. AN/FLR-9(V7) Reference Designators and Bsu/Biu Address

| Bsu/Biu<br>Address |     | Receiver    | Substation |                | Bsu/Biu |      | Receiver<br>Location |            |

|--------------------|-----|-------------|------------|----------------|---------|------|----------------------|------------|

| Dec                | Hex |             | Row        | Rack           | Row     | Rack | Row                  | Rack       |

| 0                  | 000 | 1 2         | 01         | 20             | 01      | 01   | 01<br>01             | 01U<br>01L |

| 1                  | 001 | 1 2         | 01         | 20             | 01      | 03   | 01                   | 03U<br>03L |

| 2                  | 002 | 1 2         | 01         | 20             | 01      | 07   | 01                   | 07U<br>07L |

| 3                  | 003 | 1           | 01         | 20             | 01      | 08   | 01<br>01<br>01       | 10U<br>10L |

| 4                  | 004 | 2 }         | l          | N/A*           |         |      |                      |            |

| 5                  | 005 | 2 1 2       | 01         | 20             | 01      | 12   | 01<br>01             | 12U<br>12L |

| 6                  | 006 | 2<br>1<br>2 | 01         | 20             | 01      | 13   | 01                   | 15U<br>15L |

| 7                  | 007 | 2<br>1<br>2 | 01         | 20             | 01      | 17   | 01<br>01<br>01       | 17U<br>17L |

| 8                  | 008 | 1 2         | 01         | 20             | 01      | 20   | 01<br>01<br>01       | 20U<br>20L |

| 9                  | 009 | 1 }         |            | N/A            |         |      |                      | 201        |

| 10                 | 00A | 1 2         | 02         | 18             | 02      | 01   | 02<br>02             | 01U<br>01L |

| 11                 | 00B | 1           | 02         | 18             | 02      | 03   | 02<br>02             | 05U<br>05L |

| 12                 | 00C | 2<br>1<br>2 | 02         | 18             | 02      | 06   | 02<br>02<br>02       | 06U<br>06L |

| 13                 | 00D | 1 2         | 02         | 18             | 02      | 08   | 02<br>02             | 10U<br>10L |

| 14                 | 00E | 1 }         |            | ····· N/A····· |         |      |                      |            |

| 15                 | 00F | 1 2         | 02         | 18             | 02      | 11   | 02<br>02             | 11U<br>11L |

| 16                 | 010 | 1           | 02         | 18             | 02      | 15   | 02<br>02             | 13U<br>14L |

| 17                 | 011 | 2<br>1<br>2 | 02         | 18             | 02      | 16U  | 02<br>02             | 16U<br>16L |

| 18                 | 012 | 2<br>1<br>2 | 03         | 20             | 03      | 01   | 03<br>03             | 01U<br>01L |

| 19                 | 013 | 1 2 }       |            | N/A            |         |      |                      |            |

| 20                 | 014 | 1 2         | 03         | 20             | 03      | 03   | 03<br>03             | 03U<br>03L |

<sup>\*</sup>N/A defines not assigned units.

Table 1-5. AN/FLR-9(V7) Reference Designators and Bsu/Biu Address (Continued)

|     | /Biu<br>Iress | Receiver | Subs | tation | Bsu | /Biu | Rece<br>Loca |            |

|-----|---------------|----------|------|--------|-----|------|--------------|------------|

| Dec | Hex           |          | Row  | Rack   | Row | Rack | Row          | Rack       |

| 21  | 015           | 1 2      | 03   | 20     | 03  | 07   | 03<br>03     | 07U<br>07L |

| 22  | 016           | 1 2      | 03   | 20     | 03  | 80   | 03<br>03     | 10U<br>10L |

| 23  | 017           | 1        | 03   | 20     | 03  | 12   | 03           | 12U<br>12L |

| 24  | 018           | 1 } "    |      | N/A    |     |      | 00           | 122        |

| 25  | 019           | 1 2      | 03   | 20     | 03  | 13   | 03<br>03     | 15U<br>15L |

| 26  | 01A           | 1 2      | 03   | 20     | 03  | 17   | 03<br>03     | 17U<br>18L |

| 27  | 01B           | 1 2      | 03   | 20     | 03  | 20   | 03<br>03     | 20U<br>20L |

| 28  | 01C           | 1        | 04   | 18     | 04  | о1   | 04           | 01U<br>01L |

| 29  | 01D           | 1 }      |      | N/A    |     |      |              |            |

| 30  | 01E           | 1 2      | 04   | 18     | 04  | 05   | 04<br>04     | 03U<br>03L |

| 31  | 01F           | 1 2      | 04   | 18     | 04  | 06   | 04<br>04     | 06U<br>06L |

| 32  | 020           | 1 2      | 04   | 18     | 04  | 10   | 04<br>04     | 08U<br>08L |

| 33  | 021           | 1 2      | 04   | 18     | 04  | 11   | 04<br>04     | 11U<br>11U |

| 34  | 022           | 1 } "    |      | N/A    |     |      |              |            |

| 35  | 023           | 1 2      | 04   | 18     | 04  | 15   | 04<br>04     | 13U<br>13L |

| 36  | 024           | 1 2      | 04   | 18     | 04  | 18   | 04<br>04     | 16U<br>16L |

| 37  | 025           | 1 2      | 05   | 20     | 05  | 01   | 05<br>05     | 01U<br>01L |

| 38  | 026           | 1 2      | 05   | 20     | 05  | 03   | 05<br>05     | 03U<br>03L |

| 39  | 027           | 1 2 }    |      | N/A    |     |      |              |            |

| 40  | 028           | 1<br>2   | 05   | 20     | 05  | 07   | 05<br>05     | 07U<br>10L |

| 41  | 029           | 1 2      | 05   | 20     | 05  | 08   | 05<br>05     | 10U<br>10L |

Table 1-5. AN/FLR-9(V7) Reference Designators and Bsu/Biu Address (Continued)

|     | /Biu<br>ress | Receiver         | Subst | ation | Bs  | u/Biu | Rece<br>Loca   |                   |

|-----|--------------|------------------|-------|-------|-----|-------|----------------|-------------------|

| Dec | Hex          |                  | Row   | Rack  | Row | Rack  | Row            | Rack              |

| 2   | 02A          | 1                | 05    | 20    | 05  | 12    | 05             | 12U               |

|     | _            | 2                |       |       |     |       | 05             | 12L               |

| 43  | 02B          | 1 }              | 05    | 20    | 05  | 13    | 05             | 15U               |

| 44  | 02C          | 1<br>2           |       | N/A   |     |       | 05             | 15L               |

| 45  | 02D          | 1 2              | 05    | 20    | 05  | 17    | 05<br>05       | 17U<br>17L        |

| 46  | 02E          | 1 2              | 05    | 20    | 05  | 20    | 05<br>05       | 20U<br>20L        |

| 47  | 02F          | 1 2              | 06    | 18    | 06  | 01    | 06<br>06       | 01U<br>01L        |

| 48  | 030          | 1<br>2 1         | 06    | 18    | 06  | 05    | 06<br>06       | 03U<br>03L        |

| 49  | 031          | 1 }              |       | N/A   |     |       |                | 03E               |

| 50  | 032          | 1 2              | 06    | 18    | 06  | 06    | 06<br>06       | 06U<br>06L        |

| 51  | 033          | 1 2              | 06    | 18    | 06  | 10    | 06             | 08U               |

| 52  | 034          | 1                | 06    | 20    | 06  | 11    | 06<br>06       | 08L<br>11U        |

| 53  | 035          | 2 1              | 06    | 18    | 06  | 15    | 06<br>06       | 11L<br>13U<br>13L |

| 54  | 036          | 2 }              |       | N/A   |     |       |                | IOE               |

| 55  | 037          | 2<br>1<br>2      | 06    | 18    | 06  | 18    | 06<br>06       | 16U<br>16L        |

| 56  | 038          | 1 2              | 07    | 18    | 07  | 01    | 07<br>07       | 01U<br>01L        |

| 57  | 039          | 1 2              | 07    | 18    | 07  | 05    | 07<br>07<br>07 | 03U<br>03L        |

| 58  | 03A          | 1 2              | 07    | 18    | 07  | 06    | 07<br>07<br>07 | 06U<br>06L        |

| 59  | 03B          | 1 }              |       | N/A   |     |       | 07             | UOL               |

| 60  | 03C          | 2 1              | 07    | 18    | 07  | 10    | 07<br>07       | 08U               |

| 61  | 03D          | 1<br>2<br>1<br>2 | 07    | 18    | 07  | 11    | 07             | 08L<br>11U        |

| 62  | 03E          | 1 2              | 07    | 18    | 07  | 15    | 07<br>07<br>07 | 11L<br>13U<br>13L |

Table 1-5. AN/FLR-9(V7) Reference Designators and Bsu/Biu Address (Continued)

|     | u/Biu<br>dress | Receiver         | Subs | tation | Bsu | ı/Biu   |                | eiver<br>ation    |

|-----|----------------|------------------|------|--------|-----|---------|----------------|-------------------|

| Dec | Hex            |                  | Row  | Rack   | Row | Rack    | Row            | Rack              |

| 63  | 03F            | 1 2              | 07   | 18     | 07  | 18      | 07<br>07       | 16U<br>16L        |

| 64  | 040            | 1 2 }            |      | N/A    |     |         | 07             | IOL               |

| 65  | 041            | 1 2              | 08   | 20     | 08  | 01      | 08<br>08       | 01U<br>01L        |

| 66  | 042            | 1 2              | 08   | 20     | 08  | 05<br>2 | 08<br>08       | 03U<br>03L        |

| 67  | 043            | 1 2              | 08   | 20     | 08  | 06      | 08<br>08       | 06U<br>06L        |

| 68  | 044            | 1 2              | 08   | 20     | 08  | 10      | 08<br>08       | 08U<br>08L        |

| 69  | 045            | 1 ) ·            |      | N/A    |     |         |                |                   |

| 70  | 046            | 2 <b>}</b>       | 08   | 20     | 08  | 11      | 08             | 11U               |

| 71  | 047            | 2<br>1<br>2      | 08   | 20     | 08  | 15      | 08<br>08<br>08 | 11L<br>13U<br>13L |

| 72  | 048            | 1 2              | 08   | 20     | 08  | 16      | 08<br>08       | 16U<br>16L        |

| 73  | 049            | 1 2              | 08   | 20     | 08  | 20      | 08<br>08       | 18U<br>18L        |

| 74  | 04A            | 1 Ն              |      | N/A    |     |         |                |                   |

| 75  | 04B            | 2 <b>f</b> 1 2   | 09   | 18     | 09  | 01      | 09<br>09       | 01U<br>01L        |

| 76  | 04C            | 1 2              | 09   | 18     | 09  | 05      | 09<br>09<br>09 | 03U<br>03L        |

| 77  | 04D            | 1 2              | 09   | 18     | 09  | 06      | 09<br>09       | 06U<br>06L        |

| 78  | 04E            | 1 2              | 09   | 18     | 09  | 10      | 09<br>09       | 08u<br>08L        |

| 79  | 04F            | 1 Ն              |      | N/A    |     |         |                |                   |

| 80  | 050            | 1                | 09   | 18     | 09  | 11      | 09             | 11U               |

| 81  | 051            | 2<br>1<br>2<br>1 | 09   | 18     | 09  | 15      | 09<br>09<br>09 | 11L<br>13U<br>13L |

| 82  | 052            | 1 2              | 09   | 18     | 09  | 18      | 09<br>09<br>09 | 16U<br>16L        |

| 83  | 053            | 1 2              | 10   | 20     | 10  | 01      | 10<br>10       | 01U<br>01L        |

Table 1-5. AN/FLR-9(v7) Reference Designators and Bsu/Biu Address (Continued)

| Bsu/Biu<br>Address |     | Receiver | Subst | ation | Bsı | ı/Biu | Receiver<br>Location |            |  |

|--------------------|-----|----------|-------|-------|-----|-------|----------------------|------------|--|

| Dec                | Hex |          | Row   | Rack  | Row | Rack  | Row                  | Rack       |  |

| 84                 | 054 | 1 դ      |       | N/A   |     |       |                      |            |  |

| 04                 | 034 | 2        |       | IN/A  |     |       |                      |            |  |

| 85                 | 055 | 1        | 10    | 20    | 10  | 05    | 10<br>10             | 03U<br>03L |  |

| 86                 | 056 | 1        | 10    | 20    | 10  | 06    | 10                   | 06U        |  |

| 87                 | 057 | 2        | 10    | 20    | 10  | 10    | 10<br>10             | 06L<br>08U |  |

|                    |     | 2        |       |       |     |       | 10                   | 08L        |  |

| 88                 | 058 | 1 2      | 10    | 20    | 10  | 11    | 10<br>10             | 11U<br>11L |  |

| 89                 | 059 | 2        |       | N/A   |     |       |                      |            |  |

| 90                 | 05A | 2 }      | 10    | 20    | 10  | 15    | 10                   | 13U        |  |

|                    |     | 2        |       |       |     |       | 10                   | 13L        |  |

| 91                 | 058 | 2        | 20    | N/A   | 10  | 16    | 10<br>10             | 16U<br>16L |  |

| 92                 | 05C | 1 2      | 10    | 20    | 10  | 20    | 10<br>10             | 18U<br>18L |  |

| 93                 | 05D | 1        | 11    | 18    | 11  | 01    | 11                   | 01U        |  |

| 94                 | 05E | 2        |       | N/A   |     |       |                      |            |  |

|                    |     | 21       |       |       |     | 0.5   |                      |            |  |

| 95                 | 05F | 1 1      | 11    | 18    | 11  | 05    | 11<br>11             | 03U<br>03L |  |

| 96                 | 060 | 2        | 11    | 18    | 11  | 06    | 11                   | 06u        |  |

| 97                 | 061 | 1        | 11    | 18    | 11  | 10    | 11<br>11             | 06L<br>08U |  |

| 98                 | 062 | 2        | 11    | 18    | 11  | 11    | 11<br>11             | 08L<br>11U |  |

| 90                 | 002 | 2        | 11    | 10    | 11  | 11    | 11                   | 110<br>11L |  |

| 99                 | 063 | 1 2      |       | N/A   |     |       |                      |            |  |

| 100                | 064 | 1 }      | 11    | 18    | 11  | 15    | 11                   | 13U        |  |

| 101                | 065 | 2 1      | 11    | 18    | 11  | 18    | 11<br>11             | 13L<br>16u |  |

|                    |     | 2        |       |       |     |       | 11                   | 16L        |  |

| 102                | 066 | 1 2      | 12    | 20    | 12  | 01    | 12<br>12             | 01U<br>01L |  |

| 103                | 067 | 1<br>2   | 12    | 20    | 12  | 05    | 12                   | 03U        |  |

| 104                | 068 | 1 2      |       | N/A   |     |       | 12                   | 03L        |  |

Table 1-5. AN/FLR-9(V7) Reference Designators and Bsu/Biu Address (Continued)

|     | u/Biu<br>dress | Receiver     | Subs       | tation     | Bsu | ı/Biu |                | eiver<br>ation |

|-----|----------------|--------------|------------|------------|-----|-------|----------------|----------------|

| Dec | Hex            |              | Row        | Rack       | Row | Rack  | Row            | Rack           |

| 105 | 069            | 1 2          | 12         | 20         | 12  | 06    | 12<br>12       | 06U<br>06L     |

| 106 | 06A            | 1 2          | 12         | 20         | 12  | 10    | 12<br>12<br>12 | 08U<br>08L     |

| 107 | 06B            | 1 2          | 12         | 20         | 12  | 11    | 12<br>12       | 11U<br>11L     |

| 108 | 06C            | 1 2 }        | 12         | 20         | 12  | 15    | 12<br>12       | 13U<br>13L     |

| 109 | 06D            | 1 2          |            | N/A        |     |       |                |                |

| 110 | 06E            | 1 2          | 12         | 20         | 11  | 19    | 11<br>11       | 19U<br>19L     |

| 111 | 06F            | 1 2          | 12         | 20         | 12  | 20    | 12<br>12       | 18U<br>18L     |

| 112 | 070            | 1 2          | 15         | 09         | 13  | 04    | 13<br>N/A      | 04<br>N/A      |

| 113 | 071            | 1<br>2 1 ··· | 15         | 09         | 13  | 05    | 13<br>N/A      | 05<br>N/A      |

| 114 | 072            | 1 }          |            | N/A        |     |       | 14,71          | 1 47 1         |

| 115 | 073            | 1 2          | 15         | 09         | 14  | 03    | 14<br>N/A      | 04<br>N/A      |

| 116 | 074            | 1 2          | 15         | 09         | 15  | 03    | 15<br>15       | 03U<br>03L     |

| 117 | 075            | 1 2          | 15         | 09         | 15  | 04    | 15<br>15       | 04U<br>04L     |

| 118 | 076            | 1 2          | 15         | 09         | 15  | 08    | 15<br>15       | 08U<br>08L     |

| 119 | 077            | 1 } "        |            | N/A        |     |       |                |                |

| 120 | 078            | 1 2          | 15         | 09         | 15  | 09    | 15<br>15       | 09U<br>09L     |

| 121 | 079            | 1 2          | N/A<br>N/A | N/A<br>N/A | N/A | N/A   | 16             | 04             |

| 122 | 07A            | 1 2          | N/A<br>N/A | N/A        | N/A | N/A   | 16<br>16       | 06U<br>06L     |

| 123 | 078            | 1 2          | N/A<br>N/A | N/A<br>N/A | N/A | N/A   | 16             | 07U            |

| 124 | 07C            | 1 2          |            | N/A        |     |       |                |                |

| 125 | 07D            | 1 2          | N/A        | N/A        | N/A | N/A   | 16<br>N/A      | 11U<br>N/A     |

Table 1-5. AN/FLR-9(V7) Reference Designators and Bsu/Biu Address (Continued)

|     | ı/Biu<br>Iress | Receiver        | Subs | tation | Bsu             | ı/Biu |                | eiver<br>ation |

|-----|----------------|-----------------|------|--------|-----------------|-------|----------------|----------------|

| Dec | Hex            |                 | Row  | Rack   | Row             | Rack  | Row            | Rack           |

| 126 | 07E            | 1 2             | N/A  | N/A    | N/A             | N/A   | 17<br>N/A      | 01<br>N/A      |

| 127 | 07F            | 1 2             | N/A  | N/A    | N/A             | N/A   | 17<br>N/A      | 02<br>N/A      |

| 128 | 080            | 1 2             | N/A  | N/A    | N/A             | N/A   | 17<br>17       | 06U<br>06L     |

| 129 | 081            | 1 }             |      |        | ····· N/A ····· |       |                |                |

| 130 | 082            | 1 2             | N/A  | N/A    | N/A             | N/A   | 17<br>N/A      | 12<br>N/A      |

| 131 | 083            | 1 2             | N/A  | N/A    | 18              | 01    | 18<br>18       | 01U<br>01L     |

| 132 | 084            | 1 2             | N/A  | N/A    | 18              | 04    | 18<br>18       | 06U<br>06L     |

| 133 | 085            | 1 2             | 18   | 13     | 18              | 07    | 18<br>18       | 09U<br>09L     |

| 134 | 086            | 1.              |      |        | N/A             |       |                |                |

| 135 | 087            | 2 } "<br>1<br>2 | 18   | 13     | 18              | 10    | 18<br>18       | 12U<br>12L     |

| 136 | 088            | 1 2             | 18   | 13     | 18              | 13    | 18<br>18       | 15U<br>15L     |

| 137 | 089            | 1 2             | 18   | 13     | 19              | OI    | 19<br>19       | 03U<br>03L     |

| 138 | 08A            | 1 2             | 19   | 13     | 19              | 04    | 19<br>19       | 06U<br>06L     |

| 139 | 08B            | 1               |      |        | N/A             |       | 10             | OOL            |

| 140 | 08C            | 2 }<br>1<br>2   | 19   | 13     | 19              | 19    | 07<br>19       | 19U<br>09L     |

| 141 | 08D            | 1 2             | 19   | 13     | 19              | 10    | 19<br>19       | 12U<br>12L     |

| 142 | 08E            | 1 2             | 19   | 13     | 19              | 13    | 19<br>19       | 15U<br>15L     |

| 143 | 08F            | 1 2             | 19   | 13     | 20              | 01    | 20<br>20       | 03U<br>03L     |

| 144 | 090            | 1<br>2 <b>}</b> |      |        | N/A             |       | 20             |                |

| 145 | 091            | 1 2             | 21   | 13     | 20              | 04    | 20<br>20       | 06U<br>06L     |

| 146 | 092            | 1 2             | 21   | 13     | 20              | 07    | 20<br>20<br>20 | 09U<br>09L     |

Table 1-5. AN/FLR-9(V7) Reference Designators and Bsu/Biu Address (Continued)

|     | ı/Biu<br>Iress | Receiver           | Subs | station   | Bsu | ı/Biu |                | eiver<br>ation    |

|-----|----------------|--------------------|------|-----------|-----|-------|----------------|-------------------|

| Dec | Hex            |                    | Row  | Rack      | Row | Rack  | Row            | Rack              |

|     |                |                    |      |           |     |       |                |                   |

| 147 | 093            | 1 2                | 21   | 13        | 20  | 10    | 20<br>20       | 12U<br>12L        |

| 148 | 094            | 1<br>2             | 19   | 13        | 20  | 13    | 20             | 15U<br>15L        |

| 149 | 095            | 1 } "              |      | N/A       |     |       |                |                   |

| 150 | 096            | 1<br>2             | 19   | 13        | 21  | 01    | 21<br>21       | 03U<br>03L        |

| 151 | 097            | 1<br>2             | 21   | 13        | 21  | 04    | 21<br>21       | 06U<br>06L        |

| 152 | 098            | 1 2                | 21   | 13        | 21  | 07    | 21<br>21       | 09U<br>09L        |

| 153 | 099            | 1 2                | 21   | 13        | 21  | 10    | 21<br>21       | 12U<br>12L        |

| 154 | 09A            | 1 }                |      | N/A······ |     |       | 21             | 125               |

| 155 | 09B            | 1 2                | 21   | 13        | 21  | 13    | 21<br>21       | 15U<br>15L        |

| 156 | 09C            | 1                  | 21   | 13        | 22  | 01    | 22<br>22<br>22 | 01U               |

| 157 | 09D            | 2 1                | 22   | 13        | 22  | 04    | 22             | 01L<br>06U        |

| 158 | 09E            | 2 1                | 22   | 13        | 22  | 07    | 22<br>22<br>22 | 06L<br>09U        |

| 159 | 09F            | 2<br>1<br>2 }      |      | N/A       |     |       |                | 09L               |

| 160 | 0A0            | 1                  | 22   | 13        | 22  | 10    | 22             | 12U               |

| 161 | 0A1            | 2<br>1<br>2        | 22   | 13        | 22  | 13    | 22<br>22       | 12L<br>15U        |

| 162 | 0A2            | 1                  | 22   | 13        | 23  | 01    | 22<br>23       | 15L<br>03U        |

| 163 | 0A3            | 2                  | 22   | 13        | 23  | 04    | 23<br>23       | 03L<br>06U        |

| 164 | 0A4            | 2<br>1<br>2 }····· |      | N/A       |     |       | 23             | 06L               |

| 165 | 0A5            | 1                  | 22   | 13        | 23  | 07    | 23             | 09U               |

| 166 | 0A6            | 2                  | 22   | 13        | 23  | 12    | 23<br>23       | 09L<br>12U        |

| 167 | 0A7            | 2<br>1<br>2        | 24   | 02        | 23  | 13    | 23<br>23<br>23 | 12L<br>15U<br>12L |

Table 1-5. AN/FLR-9(V7) Reference Designators and Bsu/Biu Address (Continued)

| Bsu<br>Add  |                | Receiver         | Subs                    | tation       | Bsu   | /Biu    | Rece<br>Loca | eiver<br>ation |

|-------------|----------------|------------------|-------------------------|--------------|-------|---------|--------------|----------------|

| Dec         | Hex            |                  | Row                     | Rack         | Row   | Rack    | Row          | Rack           |

| 168         | 0A8            | 1                | 24                      | 02           | 24    | 02      | 24           | 02             |

|             |                | 2                |                         |              |       |         | 24           | 03             |

| 169         | 0A9            | 1 չ              |                         | N/A          |       |         |              |                |

|             |                | 2 }              |                         |              |       |         |              |                |

| 170         | 0AA            | 1                | 24                      | 02           | 25    | 01      | 25           | 11             |

|             |                | 2                |                         |              |       |         | 25           | 02             |

| 171         | 0AB            | 1                | 24                      | 02           | 25    | 04      | 25           | 04             |

|             |                | 2                |                         |              |       |         | 25           | 05             |

| 172         | 0AC            | 1                | 24                      | 02           | 25    | 07      | 25           | 07             |

|             |                | 2                |                         |              |       |         | 25           | 80             |

| 173         | 0AD            | 1 Ն              |                         | N/A          |       |         |              |                |

|             |                | 2 5              |                         |              |       |         |              |                |

| 496         | IF0            | *                | Flash                   | Pos 1        | Flash | n Pos 1 | Flash        | Pos 1          |

| 498         | IF2            | *                | Flash Pos 1 Flash Pos 2 |              | Pos 2 | Flash   | Pos 2        |                |

| 500         | IF4            | *                | Flash Pos 3 Flas        |              |       |         | Flash        | Pos 3          |

| Only 1 rece | eiver is assoc | iated with bsu/b | iu address 4            | 96, 498, and | 500.  |         |              |                |

Table 1-6. AN/FLR 9(V8) Reference Designators and Bsu/Biu Address

|     | /Biu<br>ress | Receiver  | Subs | tation    | Bsu  | /Biu      |            | eiver<br>ation |

|-----|--------------|-----------|------|-----------|------|-----------|------------|----------------|

| Dec | Hex          |           | Row  | Rack      | Row  | Rack      | Row        | Rack           |

| 0   | 000          | 1         | 30   | 14        | 30   | 14        | 30         | 12U            |

| 1   | 001          | 2 1       | 30   | 14        | 30   | 15        | 30<br>30   | 12L<br>13U     |

| 2   | 002          | 2         | 30   | 14        | 30   | 13        | 30<br>30   | 13L<br>16U     |

| 3   | 003          | 2         | 30   | 14        | 30   | 16        | 30<br>30   | 16L<br>17U     |

| 4   | 004          | 2 1       | 30   | 14        | 31   | 11        | 30<br>31   | 17L<br>17U     |

| 5   | 005          | 2<br>Test | Loc. | <br>217A7 | Loc. | <br>217A6 | 31<br>Loc. | 11L<br>217A5   |

| 6   | 006          | 1         | 30   | 14        | 31   | 21        | 31         | 21U            |

| 7   | 007          | 2 1       | 30   | 14        | 31   | 22        | 31<br>31   | 21L<br>22U     |

| 8   | 008          | 2 1       | 33   | 10        | 32   | 01        | 31<br>32   | 22L<br>01U     |

|     |              | 2         |      |           |      |           | 32         | 01L            |

Change 2 1-14

Table 1-6. AN/FLR 9(V8) Reference Designators and Bsu/Biu Address (Continued)

| Bsu<br>Add |     | Receiver    | Subs | station | Bsu | /Biu | Rece<br>Loca | eiver<br>ation |

|------------|-----|-------------|------|---------|-----|------|--------------|----------------|

| Dec        | Hex |             | Row  | Rack    | Row | Rack | Row          | Rack           |

| 9          | 009 | 1<br>2      | 33   | 10      | 32  | 05   | 32<br>32     | 03U<br>03L     |

| 10         | 00A | 1 2         | 33   | 10      | 32  | 06   | 32<br>32     | 06U<br>06L     |

| 11         | 00B | 1 2         | 33   | 10      | 32  | 10   | 32<br>32     | 08U<br>08L     |

| 12         | 00C | 1           | 33   | 10      | 32  | 11   | 32<br>32     | 11U<br>11L     |

| 13         | 00D | 2<br>1<br>2 | 33   | 10      | 32  | 15   | 32<br>32     | 13U<br>13L     |

| 14         | 00E | 2<br>1<br>2 | 33   | 02      | 33  | 01   | 33<br>33     | 01U<br>01L     |

| 15         | 00F | 2<br>1<br>2 | 33   | 02      | 33  | 05   | 33<br>33     | 03U<br>03L     |

| 16         | 010 | 1 2         | 33   | 02      | 33  | 06   | 33<br>33     | 06U<br>06L     |

| 17         | 011 | 1 2         | 33   | 10      | 33  | 10   | 33<br>33     | 08U<br>08L     |

| 18         | 012 | 1 2         | 33   | 10      | 33  | 13   | 33<br>33     | 11U<br>11L     |

| 19         | 013 | 1<br>2      | 37   | 02      | 34  | 01   | 34<br>34     | 01U<br>01L     |

| 20         | 014 | 1<br>2      | 34   | 13      | 34  | 05   | 34<br>34     | 03U<br>03L     |

| 21         | 015 | 1 2         | 34   | 13      | 34  | 06   | 34<br>34     | 06U<br>06L     |

| 22         | 016 | 1 2         | 34   | 13      | 34  | 10   | 34<br>34     | 08u<br>08L     |

| 23         | 017 | 1 2         | 34   | 13      | 34  | 11   | 34<br>34     | 11U<br>11L     |

| 24         | 018 | 1<br>2      | 34   | 13      | 34  | 15   | 34<br>34     | 13U<br>13L     |

| 25         | 019 | 1<br>2      | 34   | 13      | 34  | 16   | 34<br>34     | 16U<br>16L     |

| 26         | 01A | 1<br>2<br>1 | 34   | 13      | 34  | 20   | 34<br>34     | 18U<br>18L     |

| 27         | 018 | 1<br>2<br>1 | 34   | 13      | 34  | 23   | 34<br>34     | 21U<br>21L     |

| 28<br>2    | 01C | 1           | 37   | 02      | 35  | 01   | 35<br>35     | 01U<br>01L     |

| 29         | 01D | 1<br>2      | 35   | 13      | 35  | 05   | 35<br>35     | 03U<br>03L     |

| 30         | 01E | 1<br>2      | 35   | 13      | 35  | 06   | 35<br>35     | 06U<br>06L     |

Table 1-6. AN/FLR 9(V8) Reference Designators and Bsu/Biu Address (Continued)

| Bsu/<br>Addr |     | Receiver    | Subs     | station | Bsu | /Biu |                | ceiver<br>cation |

|--------------|-----|-------------|----------|---------|-----|------|----------------|------------------|

| Dec          | Hex |             | Row      | Rack    | Row | Rack | Row            | Rack             |

| 31           | 01F | 1 2         | 35       | 13      | 35  | 10   | 35<br>35       | 08U<br>08L       |

| 32           | 020 | 1 2         | 35       | 13      | 35  | 11   | 35<br>35       | 11U<br>11L       |

| 33           | 021 | 1<br>2      | 35       | 13      | 35  | 15   | 35<br>35       | 13U<br>131       |

| 34           | 022 | 1           | 35       | 13      | 35  | 16   | 35<br>35       | 16U<br>16L       |

| 35           | 023 | 2<br>1<br>2 | 35       | 13      | 35  | 20   | 35<br>35       | 18U<br>18L       |

| 36           | 024 | 1           | 35       | 13      | 35  | 23   | 35<br>35       | 21U<br>21L       |

| 37           | 025 | 2<br>1<br>2 | 37       | 02      | 36  | 01   | 36<br>36       | 01U<br>01L       |

| 38           | 026 | 2<br>1<br>2 | 36       | 13      | 36  | 05   | 36<br>36       | 03U<br>03L       |

| 39           | 027 | 1 2         | 36<br>36 | 13      | 36  | 06   | 36             | 06U<br>06L       |

| 40           | 028 | 1<br>2      | 36       | 13      | 36  | 10   | 36<br>36       | 08U<br>08L       |

| 41           | 029 | 1 2         | 36       | 13      | 36  | 10   | 36<br>36       | 11U<br>11L       |

| 42           | 02A | 1 2         | 36       | 13      | 36  | 15   | 36<br>36       | 13U<br>13L       |

| 43           | 02B | 1 2         | 36       | 13      | 36  | 16   | 36<br>36       | 16U<br>16L       |

| 44           | 02C | 1 2         | 36       | 13      | 36  | 20   | 36<br>36       | 18U<br>18L       |

| 45           | 02D | 1 2         | 36       | 13      | 36  | 23   | 36<br>36       | 21U<br>21L       |

| 46           | 02E | 1 2         | 37       | 02      | 37  | 01   | 37<br>37       | 01U<br>01L       |

| 47           | 02F | 1 2         | 37       | 13      | 37  | 05   | 37<br>37       | 03U<br>03L       |

| 48           | 030 | 1           | 37       | 13      | 37  | 06   | 37<br>37       | 06U<br>06L       |

| 49           | 031 | 2<br>1<br>2 | 37       | 13      | 37  | 10   | 37<br>37       | 08U<br>08L       |

| 50           | 032 | 2 1 2       | 37       | 13      | 37  | 11   | 37<br>37<br>37 | 11U<br>11L       |

| 51           | 033 | 2 1 2       | 37       | 13      | 37  | 15   | 37<br>37<br>37 | 13U<br>13L       |

| 52           | 034 | 2<br>1<br>2 | 37       | 13      | 37  | 16   | 37<br>37<br>37 | 16U<br>16L       |

Table 1-6. AN/FLR 9(V8) Reference Designators and Bsu/Biu Address (Continued)

|     | /Biu<br>ress | Receiver         | Subs | station | Bsu/ | ————<br>Biu | Rece<br>Loca |            |

|-----|--------------|------------------|------|---------|------|-------------|--------------|------------|

| Dec | Hex          |                  | Row  | Rack    | Row  | Rack        | Row          | Rack       |

| 53  | 035          | 1                | 37   | 13      | 37   | 20          | 37           | 18U        |

|     |              | 2                |      |         |      |             | 37           | 18L        |

| 54  | 036          | 1                | 37   | 13      | 37   | 23          | 37           | 21U        |

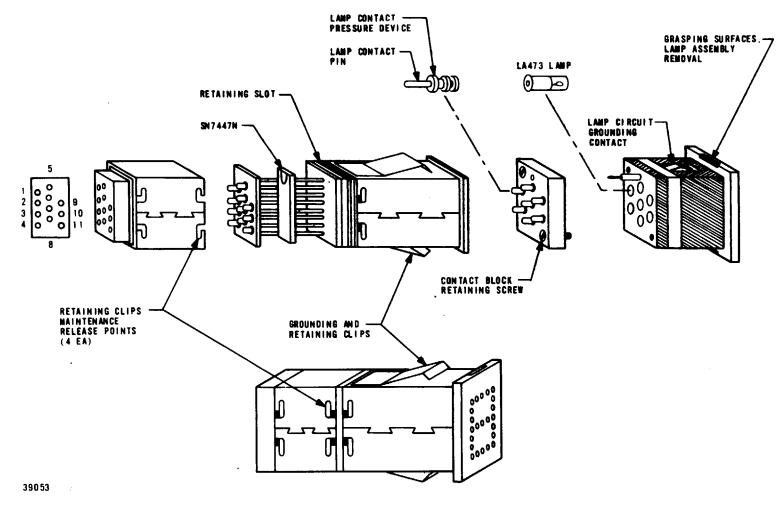

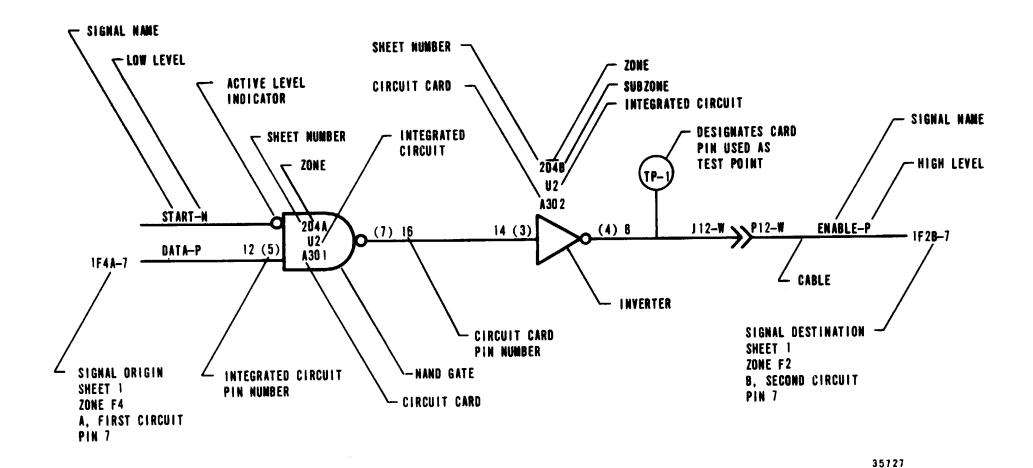

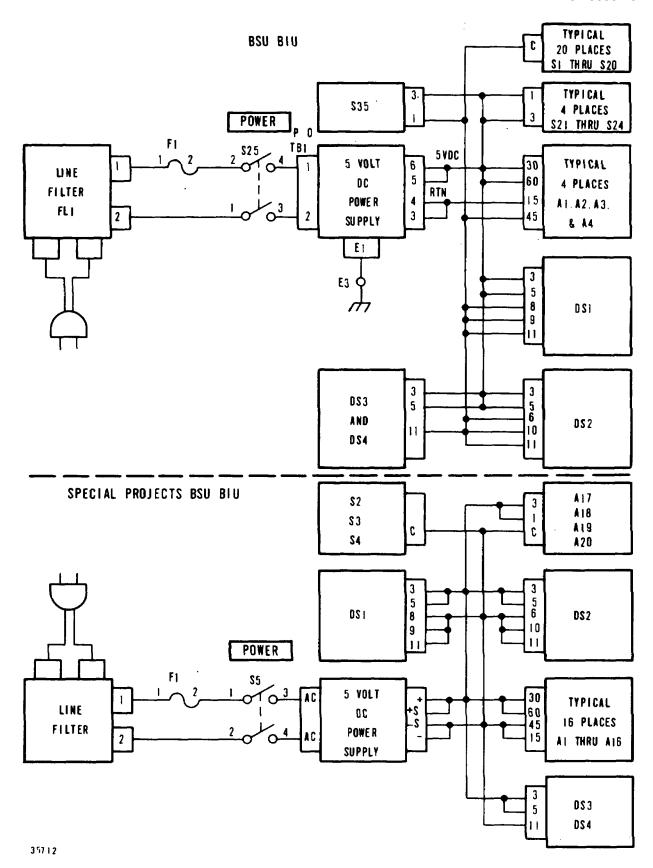

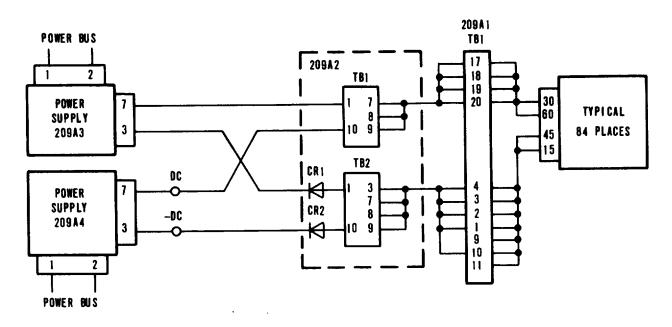

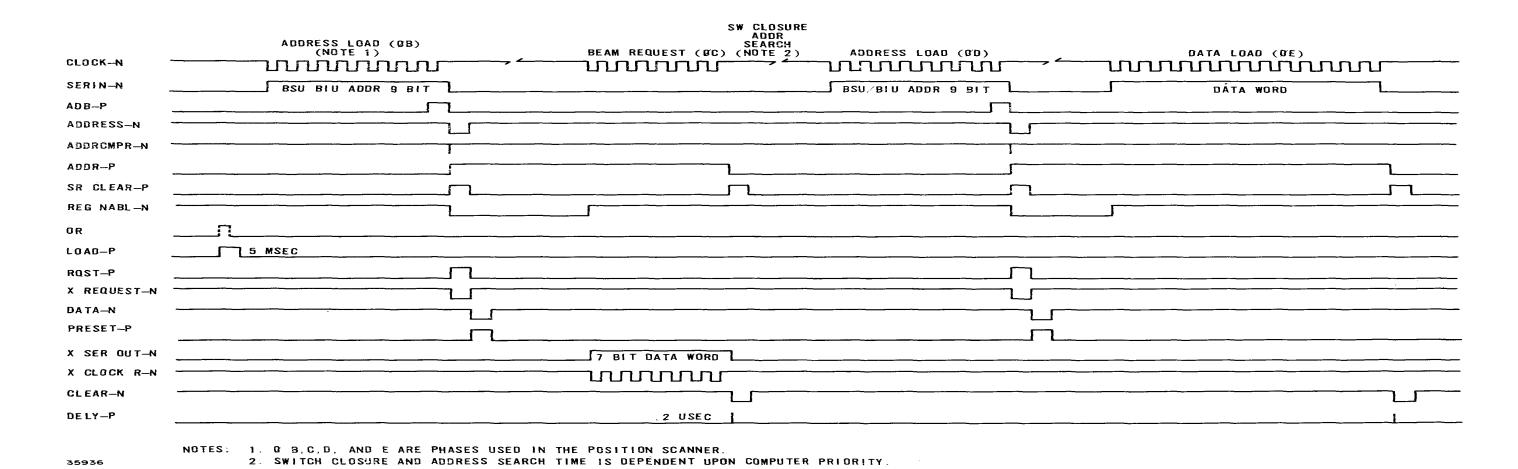

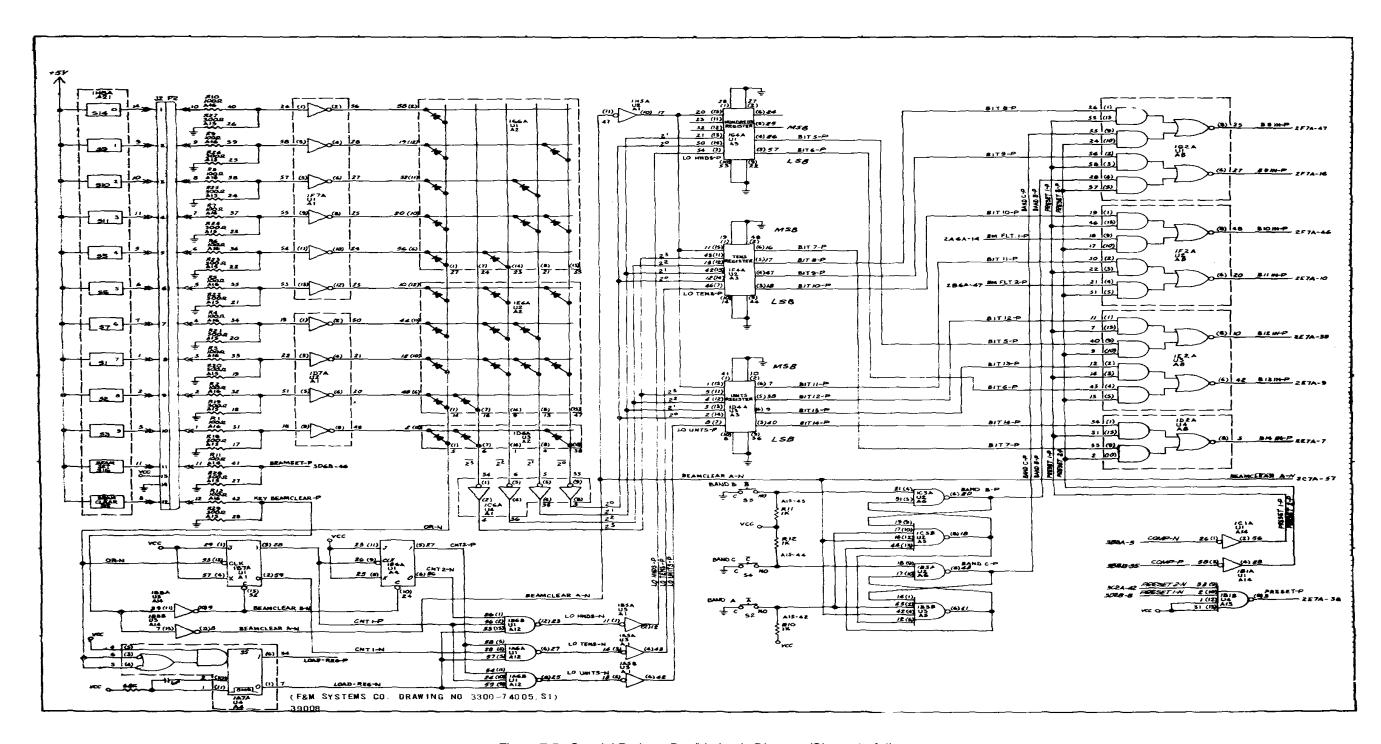

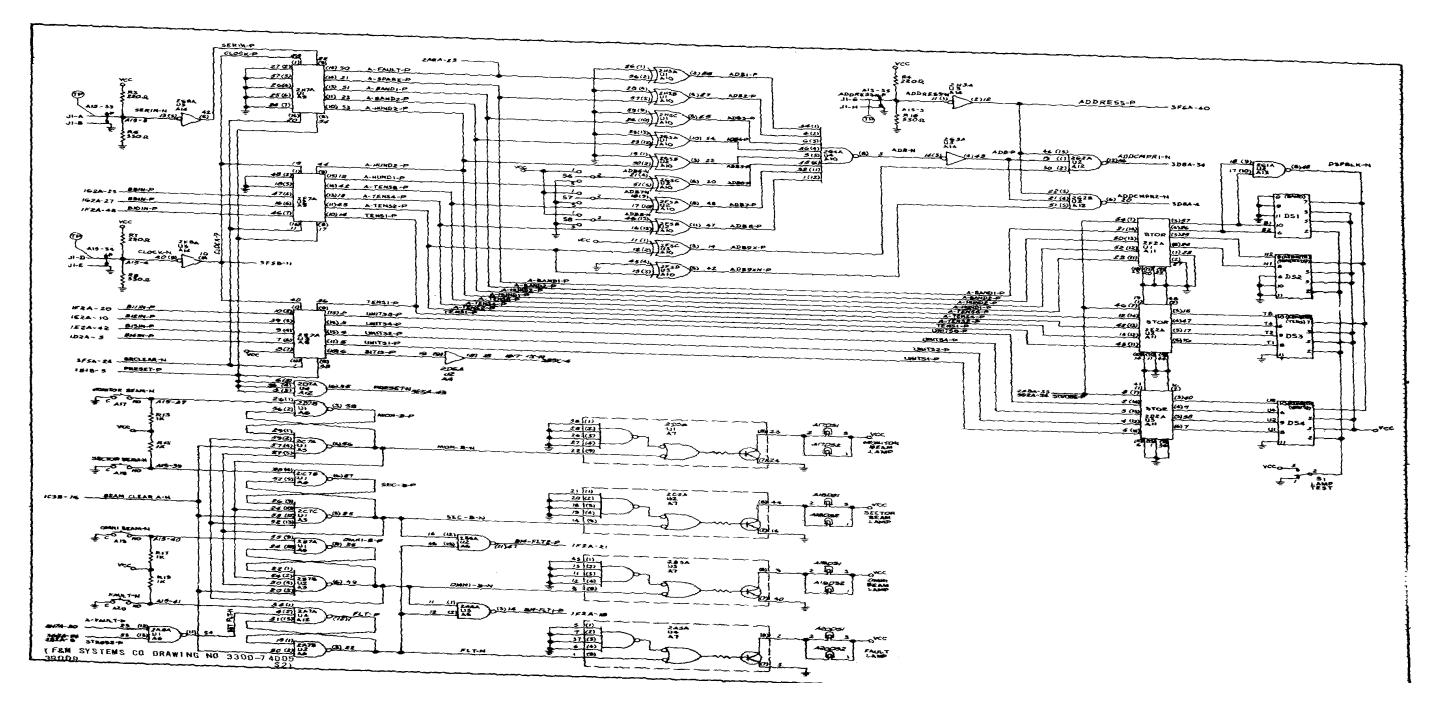

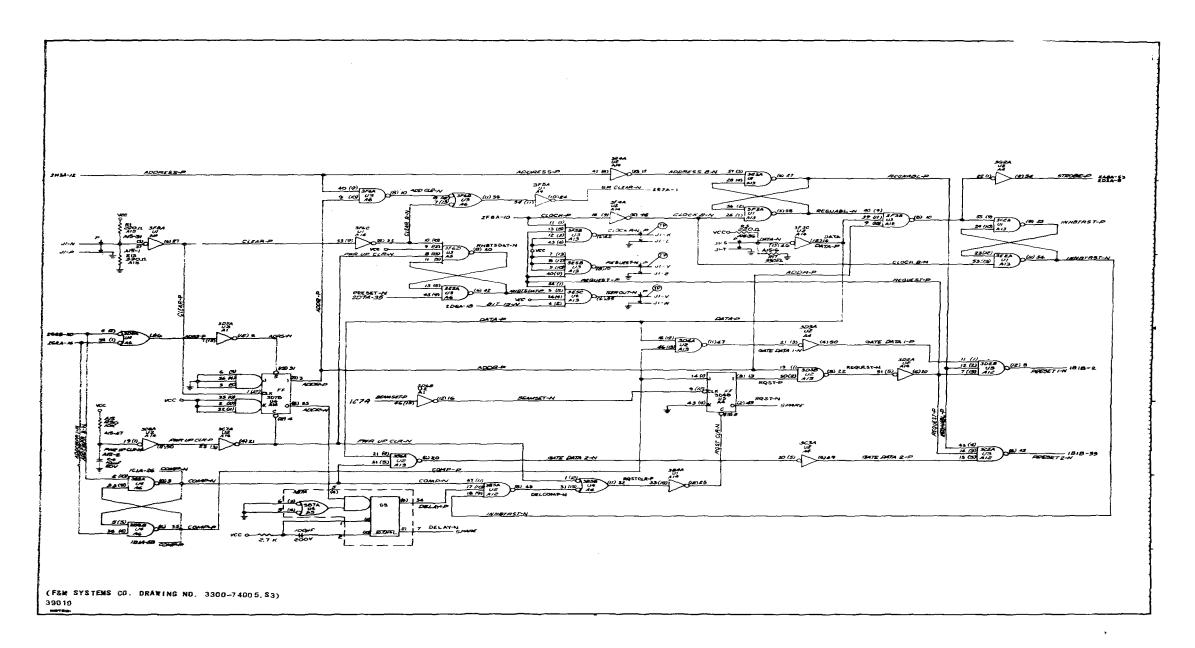

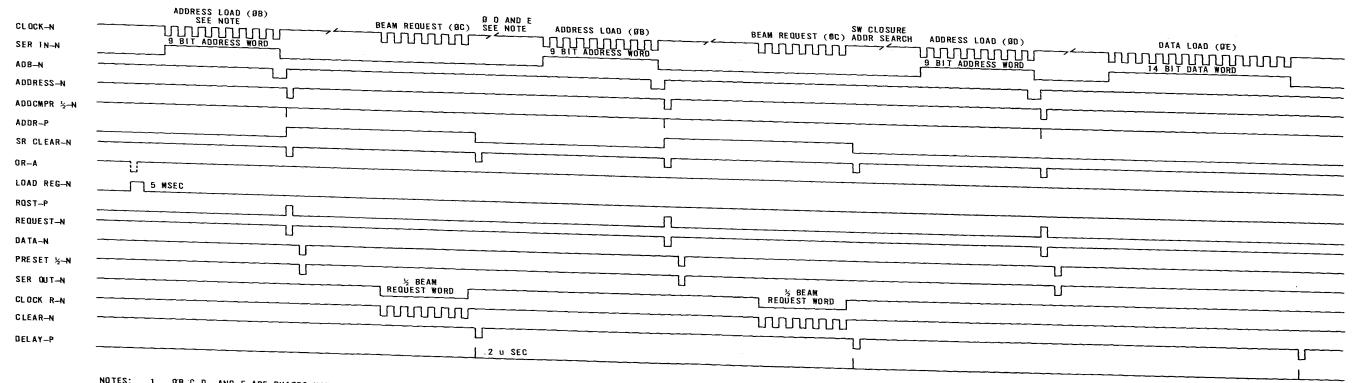

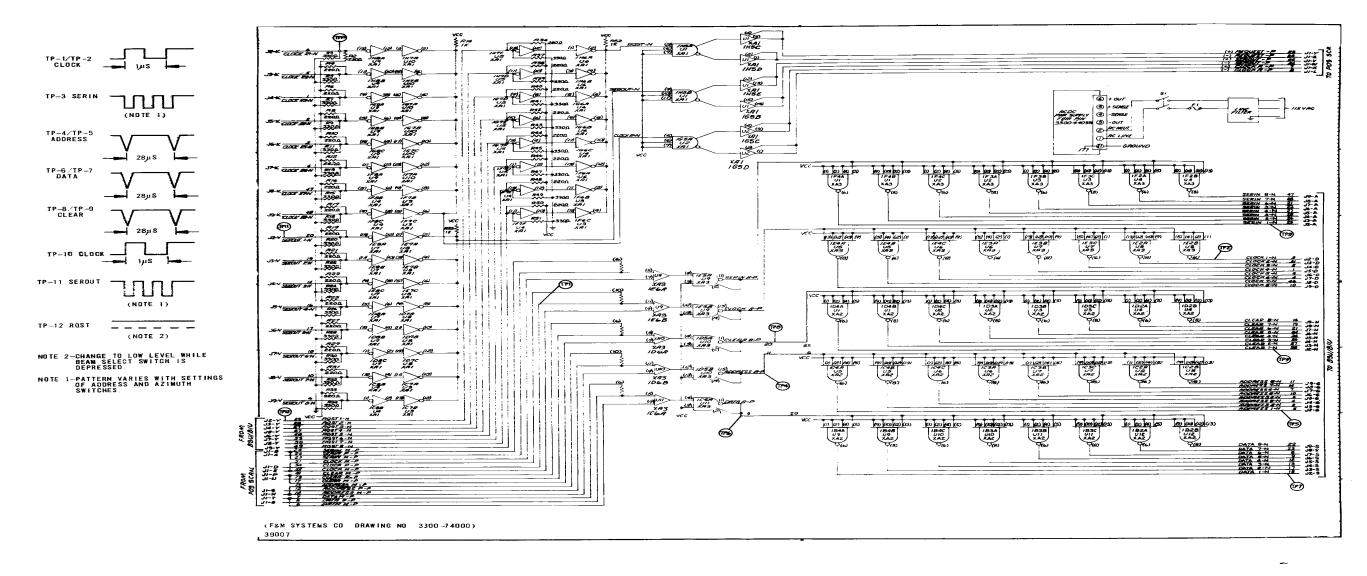

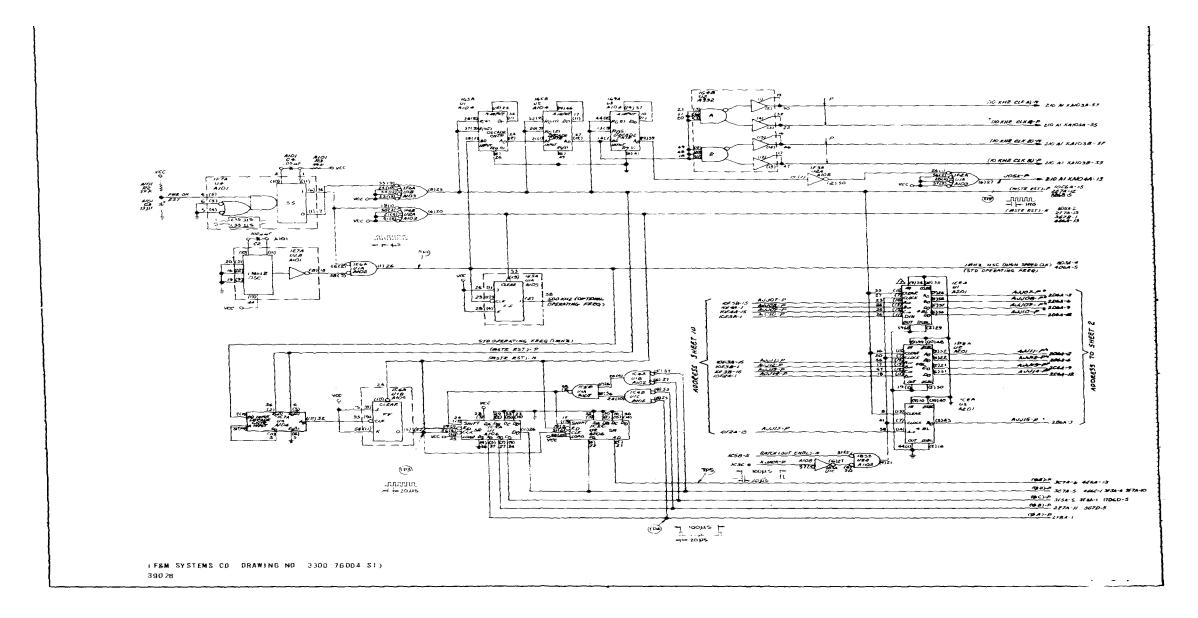

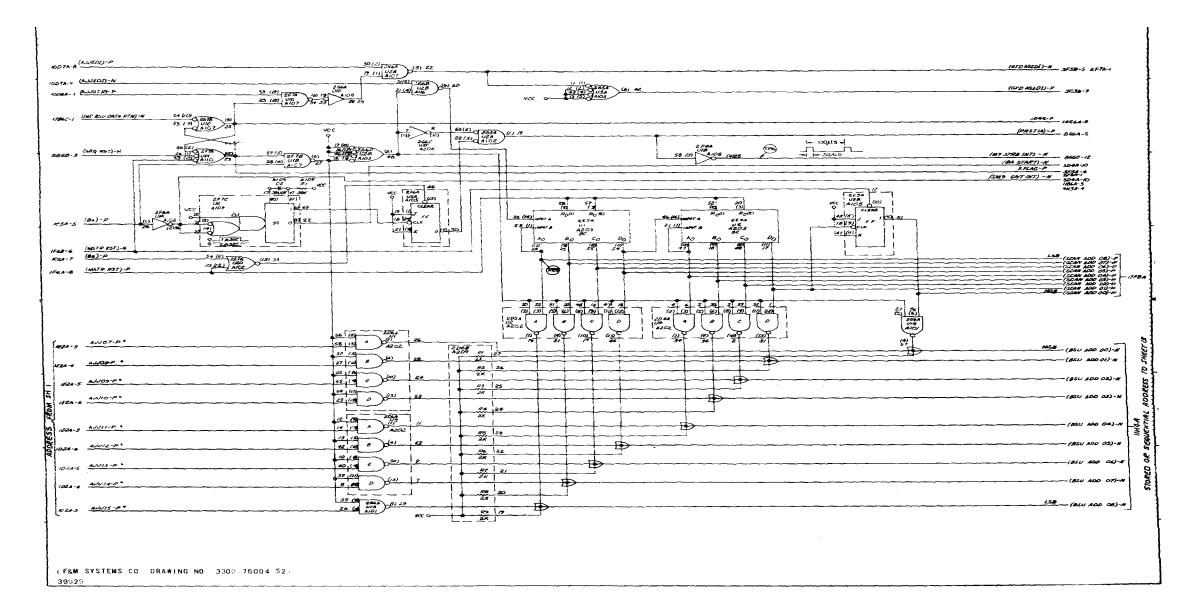

| •   |              | 2                | 0.   |         |      |             | 37           | 21L        |